# SNS COLLEGE OF TECHNOLOGY

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF MECHATRONICS ENGINEERING

19MCT201 - DESIGN OF DIGITAL CIRCUITS

II YEAR - III SEM

**UNIT 3 – SEQUENTIAL CIRCUITS**

TOPIC 2 -Counter

# **SEQUENTIAL CIRCUITS**

Latches, Edge triggered Flip flops SR, JK, T, D and Master slave – Characteristic table and equation, Application table, Synchronous counters, Design of synchronous counters, up/down counter, Modulo–n counter, Decade counters. Design of Sequential circuits using simulation

# Flip flops

| FLIP-FLOP NAME | FLIP-FLOP SYMBOL   | CHARACTERISTIC TABLE                                                                                                                                                                                 | CHARACTERISTIC<br>EQUATION                                                   | EXCITATION TABLE                                                                                                                                                                                                                                                |  |  |  |

|----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SR             | S Q<br>CIk<br>R Q' | S         R         Q(next)           0         0         Q           0         1         0           1         0         1           1         1         ?              J         K         Q(next) | $Q_{(next)} = S + R'Q$ $SR = 0$                                              | Q         Q(next)         S         R           0         0         0         X           0         1         1         0           1         0         0         1           1         1         X         0             Q         Q(next)         J         K |  |  |  |

| JK             | J Q<br>            | 0         0         Q           0         1         0           1         0         1           1         1         Q'                                                                               | $\mathbf{Q}_{(\text{next})} = \mathbf{J}\mathbf{Q'} + \mathbf{K'}\mathbf{Q}$ | 0         0         0         X           0         1         1         X           1         0         X         1           1         1         X         0                                                                                                   |  |  |  |

| D              | D Q<br>>CIk<br>Q'  | D         Q(next)           0         0           1         1                                                                                                                                        | $\mathbf{Q}_{(\mathrm{next})} = \mathbf{D}$                                  | Q         Q(next)         D           0         0         0           0         1         1           1         0         0           1         1         1                                                                                                     |  |  |  |

| T              | T Q  CIk  Q'       | T         Q(next)           0         Q           1         Q'                                                                                                                                       | $\mathbf{Q}_{(\text{next})} = \mathbf{T}\mathbf{Q'} + \mathbf{T'}\mathbf{Q}$ | Q         Q(next)         T           0         0         0           0         1         1           1         0         1           1         1         0                                                                                                     |  |  |  |

A counter is a register capable of counting the number of clock pulses arriving at its clock input. Count represents the number of clock pulses arrived. A specified sequence of states appears as the counter output. This is the main difference between a register and a counter. A specified sequence of states is different for different types of counters.

There are two types of counters, synchronous and asynchronous.

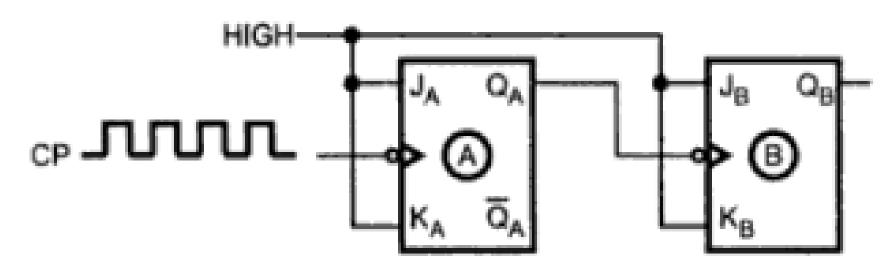

A two-bit asynchronous binary counter

# **Design of Synchronous Counter**

- Obtain the transition table from the given circuit information.

- Determine the number of flip-flops needed.

- Choose the type of flip-flops to be used.

- 4. From the transition table, derive the circuit excitation table.

- Use K-map or any other simplification method to derive the circuit the flip-flop input functions.

- Draw the logic diagram.

# Synchronous Decade Counter

#### **Excitation Table**

| Present State |                |    |                | Next State       |                    |                  | Flip-flop inputs   |                |                |    |    |

|---------------|----------------|----|----------------|------------------|--------------------|------------------|--------------------|----------------|----------------|----|----|

| QD            | Q <sub>C</sub> | QB | Q <sub>A</sub> | Q <sub>D+1</sub> | Q <sub>C + 1</sub> | Q <sub>B+1</sub> | Q <sub>A + 1</sub> | T <sub>D</sub> | T <sub>C</sub> | TB | TA |

| 0             | 0              | 0  | 0              | 0                | 0                  | 0                | 1                  | 0              | 0              | 0  | 1  |

| 0             | 0              | 0  | 1              | 0                | 0                  | 1                | 0                  | 0              | 0              | 1  | 1  |

| 0             | 0              | 1  | 0              | 0                | 0                  | 1                | 1                  | 0              | 0              | 0  | 1  |

| 0             | 0              | 1  | 1              | 0                | 1                  | 0                | 0                  | 0              | 1              | 1  | 1  |

| 0             | 1              | 0  | 0              | 0                | 1                  | 0                | 1                  | 0              | 0              | 0  | 1  |

| 0             | 1              | 0  | 1              | 0                | 1                  | 1                | 0                  | 0              | 0              | 1  | 1  |

| 0             | 1              | 1  | 0              | 0                | 1                  | 1                | 1                  | 0              | 0              | 0  | 1  |

| 0             | 1              | 1  | 1              | 1                | 0                  | 0                | 0                  | 1              | 1              | 1  | 1  |

| 1             | 0              | 0  | 0              | 1                | 0                  | 0                | 1                  | 0              | 0              | 0  | 1  |

| 1             | 0              | 0  | 1              | 0                | 0                  | 0                | 0                  | 1              | 0              | 0  | 1  |

| 1             | 0              | 1  | 0              | X                | Х                  | Х                | x                  | X              | Х              | X  | X  |

| 1             | 0              | 1  | 1              | Х                | Х                  | Х                | X                  | х              | х              | х  | ×  |

| 1             | 1              | 0  | 0              | х                | х                  | х                | Х                  | X              | х              | х  | X  |

| 1             | 1              | 0  | 1              | х                | Х                  | х                | х                  | х              | х              | х  | х  |

| 1             | 1              | 1  | 0              | х                | Х                  | х                | ×                  | х              | х              | х  | х  |

| 1             | 1              | 1  | 1              | х                | Х                  | х                | X                  | х              | х              | х  | х  |

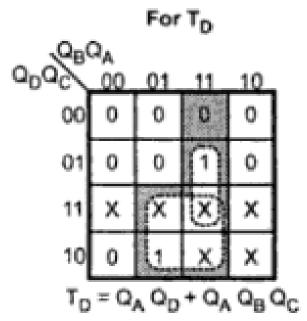

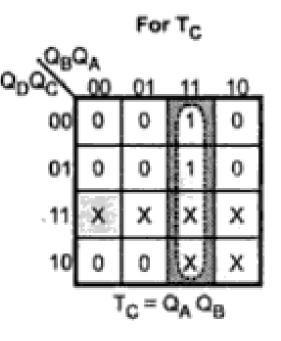

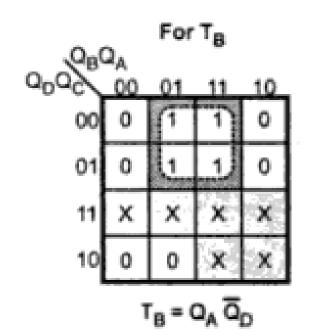

#### K-map Simplification

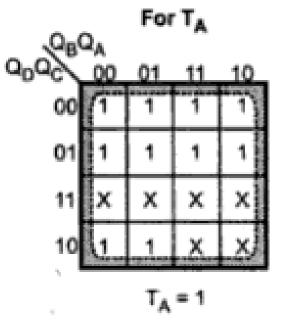

#### Logic Diagram

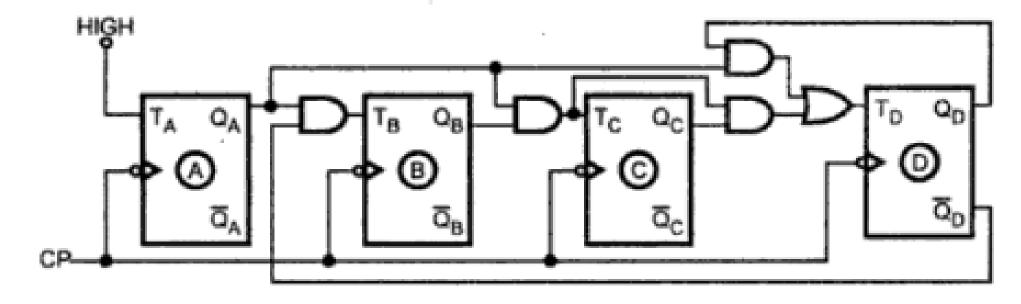

#### **Timing Diagram**

#### **ASSESSMENT - 1**

### Mux relates with us....

# Question 1

Which combinational circuit is renowned for selecting a single input from multiple inputs & directing the binary information to output line?

- ▶ a) Data Selector

- ▶ b) Data distributor

- c) Both data selector and data distributor

- ▶ d) DeMultiplexer

# Question 2

Which is the major functioning responsibility of the multiplexing combinational circuit?

- a) Decoding the binary information

- ▶ b) Generation of all minterms in an output function with OR-gate

- ▶ c) Generation of selected path between multiple sources and a single destination

- d) Encoding of binary information

# References

- <a href="https://brilliant.org/wiki/de-morgans-laws/">https://brilliant.org/wiki/de-morgans-laws/</a>

- <a href="https://circuitglobe.com/demorgans-theorem.html">https://circuitglobe.com/demorgans-theorem.html</a>

- <a href="https://www.electrical4u.com/">https://www.electrical4u.com/</a>