# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF MECHATRONICS ENGINEERING**

### **19MCT201 - DESIGN OF DIGITAL CIRCUITS** II YEAR - III SEM

### **UNIT 5 – DIGITAL LOGIC FAMILIES AND PLD**

TOPIC 5– PLD

# **Why Programmable Logic Devices?**

- Facts:

- It is most economical to produce an IC in large volumes

- Many designs required only small volumes of ICs

- Need an IC that can be:

- Produced in large volumes

- Handle many designs required in small volumes

- A programmable logic part can be:

- made in large volumes

- programmed to implement large numbers of different low-volume designs

- Many programmable logic devices are *fieldprogrammable*, i. e., can be programmed outside of the manufacturing environment

- Most programmable logic devices are *erasable* and reprogrammable.

- Allows "updating" a device or correction of errors

- Allows reuse the device for a different design the ultimate in re-usability!

- Ideal for course laboratories

- Programmable logic devices can be used to prototype design that will be implemented for sale in regular ICs.

- Complete Intel Pentium designs were actually prototype with specialized systems based on large numbers of VLSI programmable devices!

# **Types of PLD**

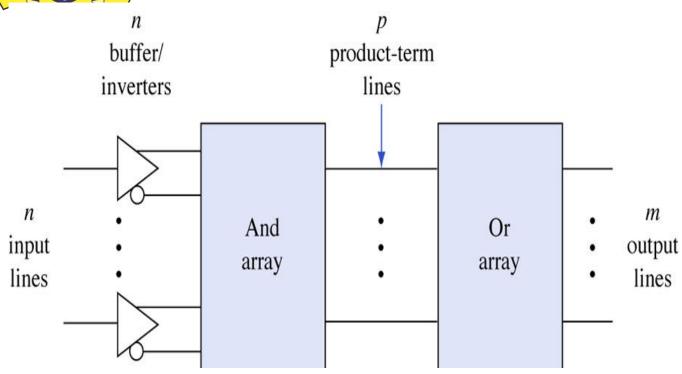

- The purpose of a PLD device is to permit elaborate digital logic designs to be implemented by the user in a single device.

- Can be erased electrically and reprogrammed with a new design, making them very well suited for academic and prototyping

- NOR, NAND)

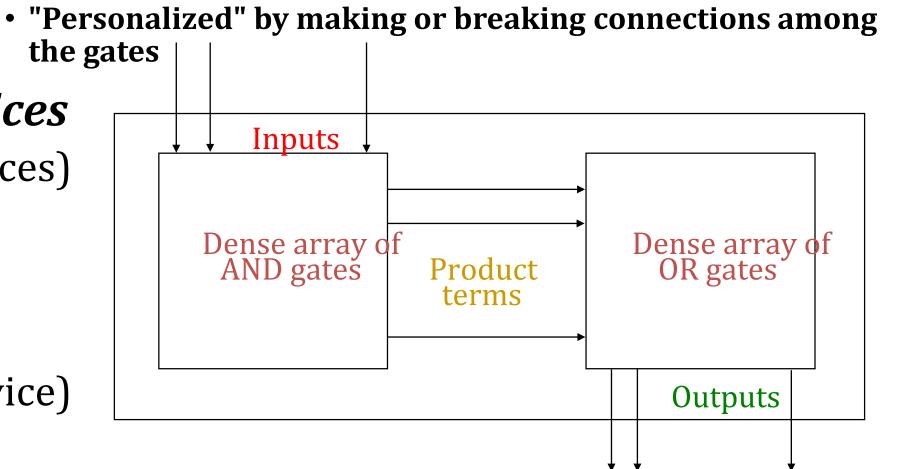

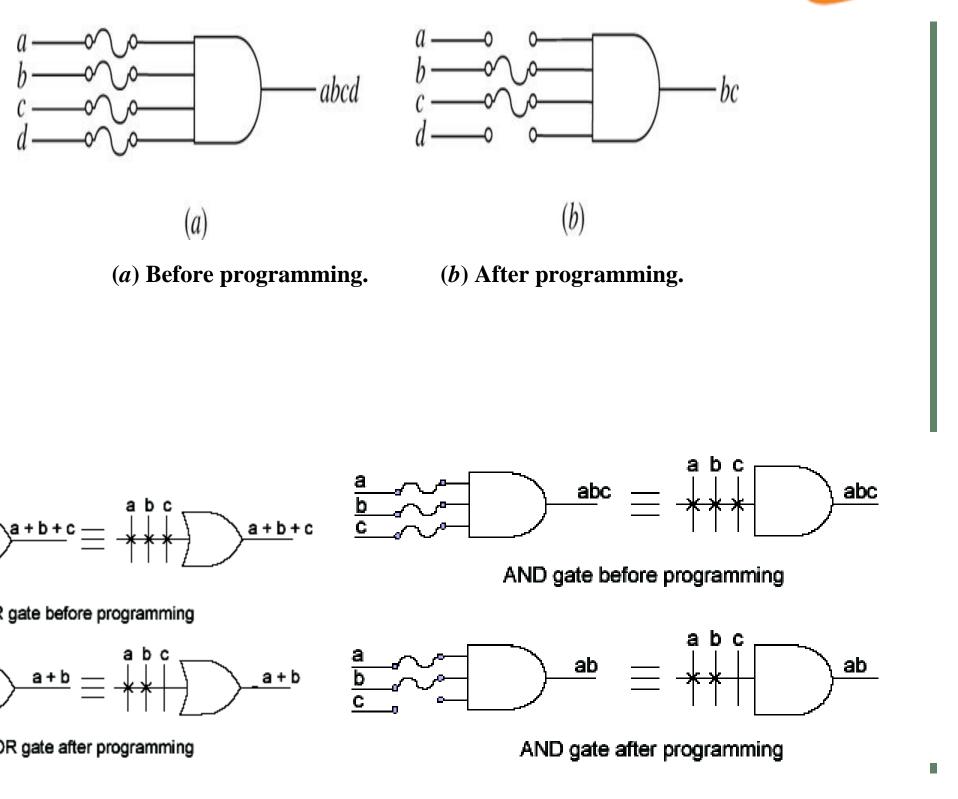

- the gates

# • Types of Programmable Logic Devices

- SPLDs (Simple Programmable Logic Devices)

- PROM (Programmable Read-Only Memory)

- PLA (Programmable Logic Array)

- PAL (Programmable Array Logic)

- GAL (Generic Array Logic)

- CPLD (Complex Programmable Logic Device)

- FPGA (Field-Programmable Gate Array)

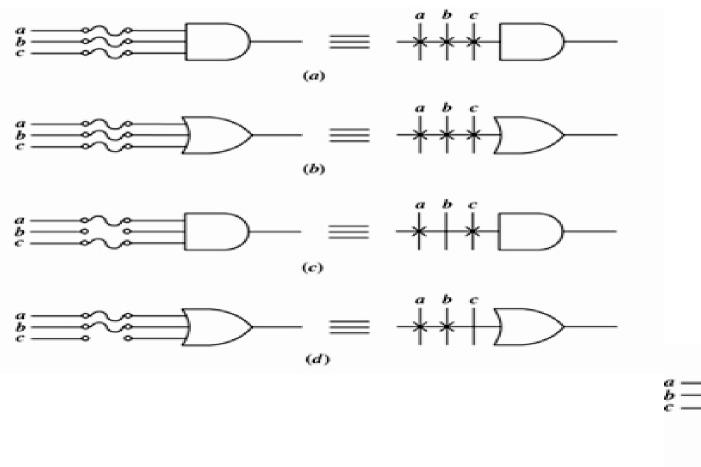

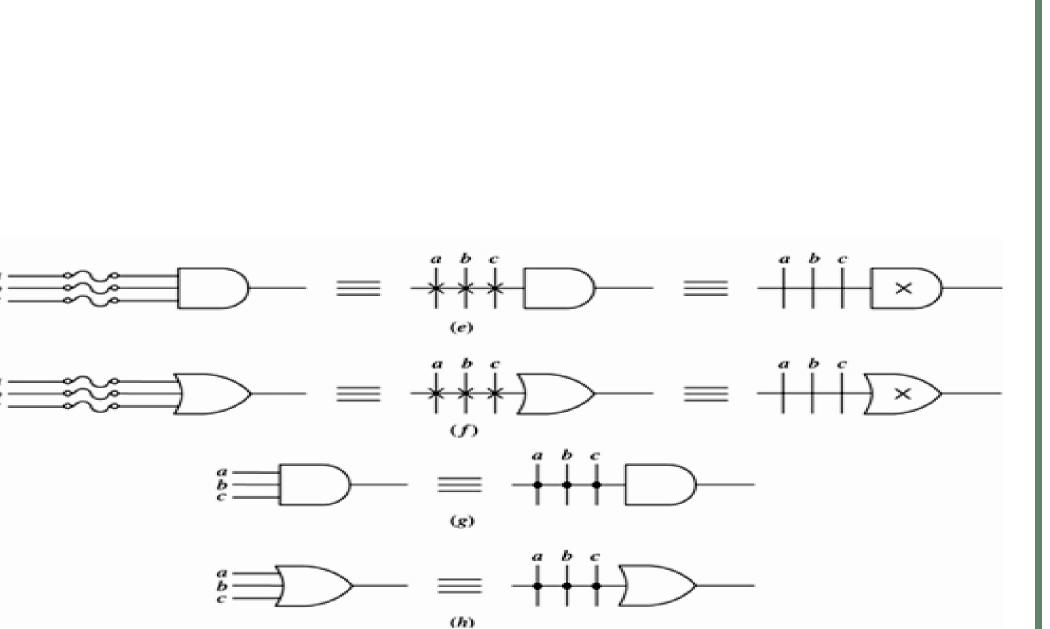

#### • Pre-fabricated building block of many AND/OR gates (or

# **Types of PLD**

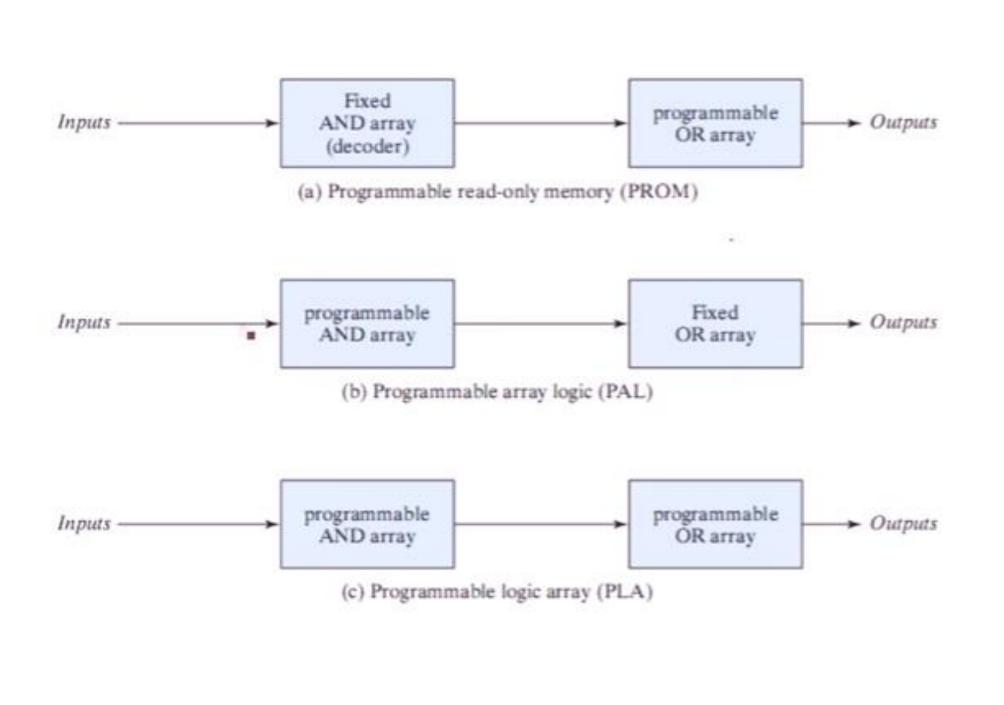

- The differences between the first three categories are these:

- In a ROM, the input connection matrix is hardwired. The user can modify the output connection matrix.

- In a PAL/GAL the output connection matrix is hardwired. The user can modify the input connection matrix.

- In a PLA the user can modify both the input connection matrix and the output connection matrix.

# **Dynamic RAM (DRAM)**

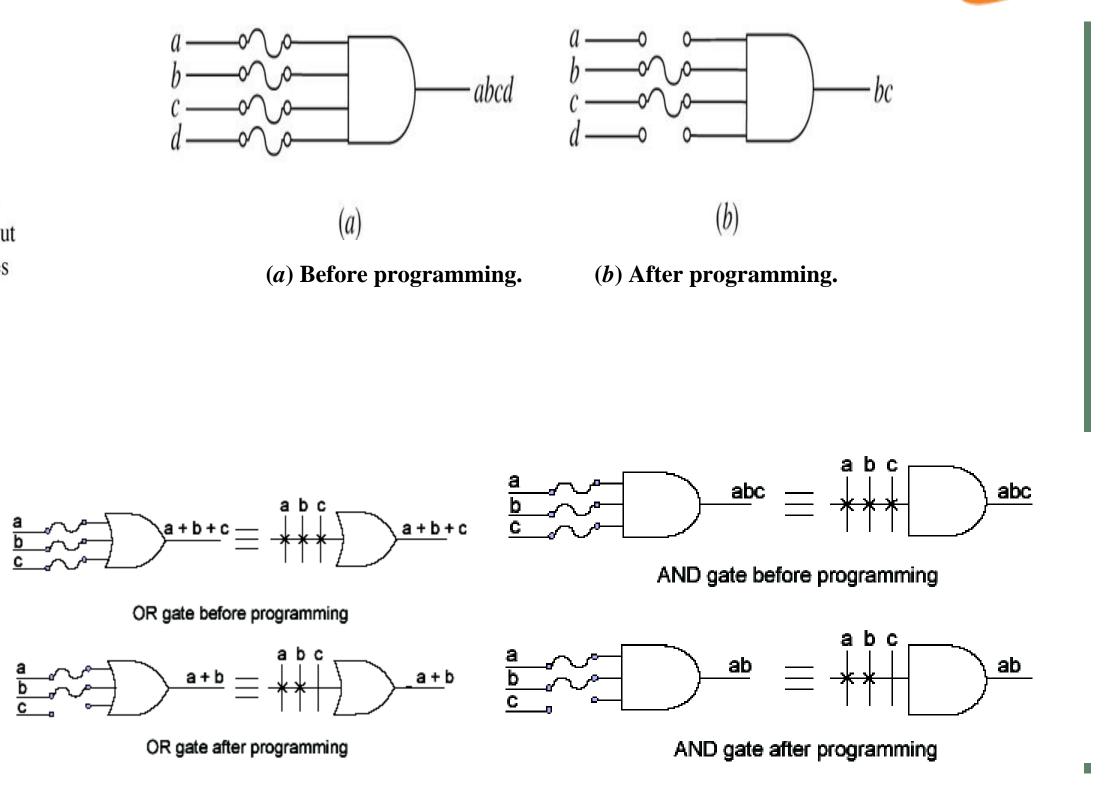

# **PLD Programming**

DIGITAL LOGIC FAMILIES/DESIGN OF DIGITAL CIRCUITS/R.YASODHARAN/MCT/SNSCT

6/8

## **ASSESSMENT - 1**

### Mux relates with us....

#### Question 1 Which combinational circuit is renowned for selecting a single Which is the major functioning responsibility of the input from multiple inputs & directing the binary information multiplexing combinational circuit? to output line? ▶ a) Data Selector a) Decoding the binary information ▶ b) Data distributor **b**) Generation of all minterms in an output function with OR-gate **c**) Both data selector and data distributor **c**) Generation of selected path between multiple sources and a single destination ▶ d) DeMultiplexer d) Encoding of binary information MULTIPLEXER/DESIGN OF DIGITAL CIRCUITS/R.YASODHARAN/MCT/SNSCT 6/16/2020

### **Question 2**

# References

- <u>https://brilliant.org/wiki/de-morgans-laws/</u>

- <u>https://circuitglobe.com/demorgans-theorem.html</u>

- https://www.electrical4u.com/ ullet