#### SNS COLLEGE OF TECHNOLOGY

(An Autonomous Institution)

COIMBATORE-35

Accredited by NBA-AICTE and Accredited by

NAAC – UGC with A+ Grade

Approved by AICTE, New Delhi & Affiliated to

Anna University, Chennai

#### DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

COURSE NAME: 19EEB303 - MICROCONTROLLER AND ITS

APPLICATIONS

III YEAR / VI SEMESTER

**Unit 2 – PIC MICROCONTROLLER**

FIGURE 3-1: PIC16F8X BLOCK DIAGRAM Data Bus Program Counter Flash/ROM EEPROM Data Memory Program Memory PIC16F83/CR83 RAM **EEPROM** 512 x 14 File Registers 8 Level Stack EEDATA Data Memory PIC16F83/CR83 PIC16F84/CR84 (13-bit) 64 x 8 36 x 8 1K x 14 PIC16F84/CR84 68 x 8 Program Bus 14 RAM Addr EEADR Addr Mux Instruction reg TMR0 Indirect Direct Addr Addr FSR reg RA4/T0CKI STATUS reg MUX Power-up I/O Ports Timer 8 Instruction Oscillator Decode & Start-up Timer ALU Control Power-on RA3:RA0 Reset Watchdog Timing RB7:RB1 W reg Timer Generation

OSC2/CLKOUT

OSC1/CLKIN

VDD, Vss

MCLR

RB0/INT

- The term **PIC** stands for

- "Peripheral Interface Controller"

# Salient teatures

- Speed: PIC executes most of its instructions in 0.2 μs or five instructions per microsecond.

- Instruction set Simplicity: just 35 instructions.

- Integration of operational features:

- **Power-on-reset** and **brown-out protection** ensure that the chip operates only when the supply voltage is within specifications.

- Watch dog timer: resets the PIC if the chip malfunctions or deviates from its normal operation at any time.

- Powerful output pin control:

- single instruction can select and drive a single output pin high or low in its 0.2 μs instruction execution time. The PIN can drive a load of up to 25μA.

# • I/O port expansion:

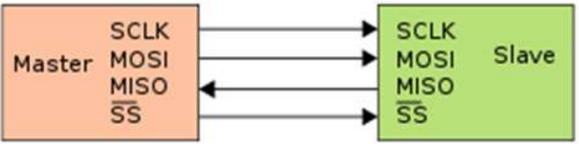

With the help of built in **Serial Peripheral Interface (SPI)** the number of I/O ports can be expanded. EPROM/DIP/ROM options are provided.

#### • Interrupt control:

Up to 12 independent interrupt sources can control when the CPU will deal with each sources.

- Programmable timer options:

- Three timers can characterize inputs, control outputs and provide internal timing for the program execution.

- There are Three Timers: Namely Timer 0, Timer1, Timer 2

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1:16-bit timer/counter with prescaler can be incremented during sleep via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, pre- scaler and post- scaler

- CPU is manufactured in RISC.

- RISC stands for Reduced Instruction Set Computer.

- Capable of recognizing and executing only 35 simple instructions.

- Execution time instructions = 4 clock cycles.

- Execution time of each instruction = 200nS

- Jump and branch instructions the execution time = 2 clock cycles.

- Operating frequency = 20MH.

- Execute 5 million instructions / second

#### The CPU registers are

- Working Register (W)

- Status Register

- FSR File Select Register

- INDF

- PCLATH

- Program Counter

- PCL

- Eight Level Stack

- All SFR in PIC are \_\_\_8\_\_ bits size

### **Working Register:(W)**

**Temporary holding** register.

Called as Accumulator.

Cannot be access Directly

W content moved to some other register and then it can be accessed.

used by many instructions as source of an operand. destination for the result of instruction execution. It is a 8-bit regarding.

11

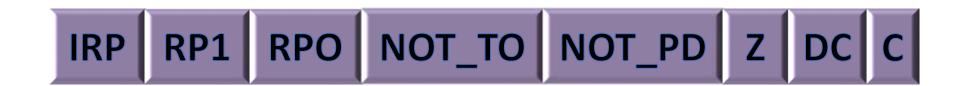

**Status Register:** can be destination for any instruction

contains: arithmetic status of the ALU

reset Status, bank select bits for data memory.

12

# FSR – (File Select Register): Special Purpose Register

- Indirect addressing.

- 8-bit register file address pointer

- any address is first written in FSR access entire register file.

#### INDF – (Indirect File): Special Purpose Register

- Is not a Physical Register

- Addressing INDF Addresses Register address in FSR

**Program Counter: (PC)**

13 bit wide

**PCL 8 Bit – Readable**

**PCH 5 Bit – Not Readable**