### SNS COLLEGE OF TECHNOLOGY

(An Autonomous Institution)

COIMBATORE-35

Accredited by NBA-AICTE and Accredited by NAAC – UGC with A++ Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

19EET103 / ELECTRIC CIRCUITS AND ELECTRON DEVICES

UNIT 4- ELECTRONIC DEVICES AND APPLICATIONS

23EET103 / ECED

DR.MVP / PROFESSOR & SENIOR INNOVATOR (CFC)

- Field Effect Transistor (FET)

- Junction Field Effect Transistor (JFET)

- Construction of JFET

- Theory of Operation

- I-V Characteristic Curve

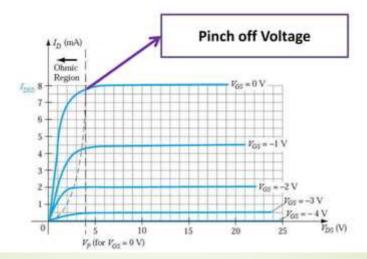

- Pinch off Voltage (VP)

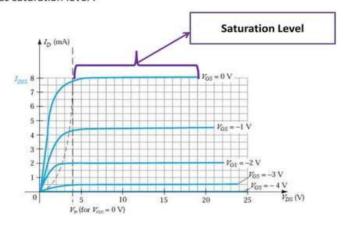

- Saturation Level

- Break Down Region

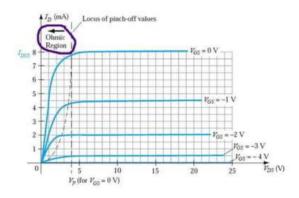

- Ohmic Region

- Cut off Voltage

- Advantages

- Disadvantages

- Application of JFET

#### INTRODUCTION

The ordinary or bipolar transistor has two main disadvantage.

- · It has a low input impedance

- · It has considerable noise level

To overcome this problem Field effect transistor (FET) is introduced because of its:

- · High input impedance

- · Low noise level than ordinary transistor

And Junction Field Effect Transistor (JFET) is a type of FET.

- > It consists of three terminal .

- Gate

- Source

- Drain

- It is classified as four types.

Typical Field Effect Transistor

JFET MOSFET

MESFET MISFET

□ Junction Field Effect Transistor is a three terminal semiconductor device in which current conducted by one type of carrier i.e. by electron or hole.

Junction field effect transistor

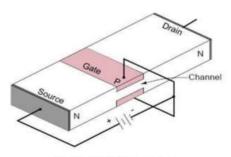

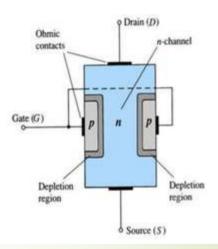

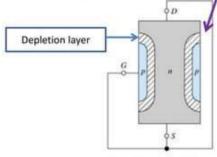

#### Construction of JFET

☐ Source: The terminal through which the majority carriers enter into the channel, is called the source terminal S.

☐ Drain: The terminal, through which the majority carriers leave from the channel, is called the *drain* terminal D.

☐ Gate: There are two internally connected heavily doped impurity regions to create two P-N junctions. These impurity regions are called the gate terminal G.

☐ Channel: The region between the source and drain, sandwiched between the two gates is called the *channel*.

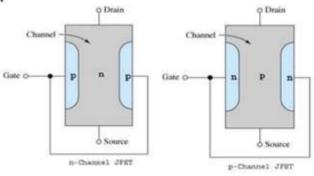

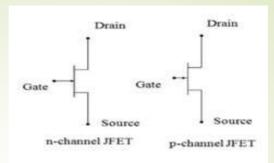

#### > JFET has two types:

- n- Channel JFET

- p- Channel JFET

# Symbol of JFET

#### **Features of JFET**

- JFET is a voltage controlled device i.e. input voltage (VGS) control the output current (ID).

- In JFETs, the width of a junction is used to control the effective crosssectional area of the channel through which current conducts.

- It is always operated with Gate-Source p-n junction in reverse bias.

- Because of reverse bias it has high input impedance.

- In JFET the gate current is zero i.e. IG=0.

8

DR.MVP / PROFESSOR & SENIOR INNOVATOR (CFC)

### Theory of Operation

- (i) When gate-source voltage(VGS) is applied and drain-source voltage is zero i.e. VDS= OV

- When VGS = 0v , two depletion layers & channel are formed normally.

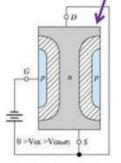

- When VGs increase negatively i.e. OV > VGS > VGS(off), depletion layers are also increased and channel will be decrease.

When VGs=VGS(off), depletion layer will touch each other and channel will totally removed. So no current can flow through the channel.

(a) Bias is zero and depletion layer is thin hence channel resistance is low.

(b) Vos is applied hence depletion layer is increased. So less charge can be flow through the channel. 00

(c) Vox is genter than cut off voltage hence no coductive path exist.

# **Theory of Operation**

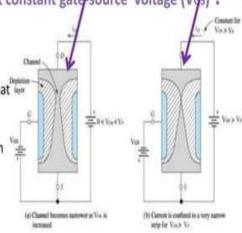

(ii) When drain-source voltage (Vos) is applied at constant gate-source voltage (Vos):

Now reverse bias at the drain end is larger than source end and so the depletion layer is wider at the drain end than source end.

When Vos increases i.e. Ov < Vos < VP, depletion layer at larger and drain end is gradually increased and drain current also increased.</p>

When Vos = VP the channel is effectively closed at drain end and it does not allow further increase of drain current. So the drain current will become constant.

- For VGs=0v the drain current is maximum. It's denoted as loss and called shorted gate drain current.

- Then if Vos increases Drain current In decreases (In < Inss) even though Vos is increased.</p>

- When VGS reaches a certain value, the drain current will be decreased to zero.

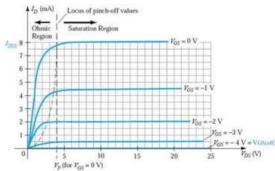

- For different Vgs, the Ip will become constant after pinch off voltage (VP) though Vps is increased.

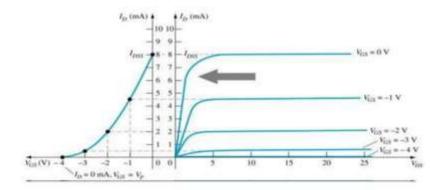

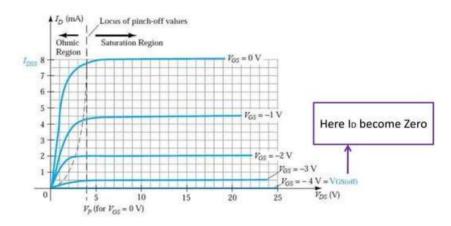

#### **Transfer Characteristic Curve**

☐ This curve shows the value of I<sub>D</sub> for a given value of V<sub>GS</sub>.

Fig: Transfer Characteristic Curve

☐ The region behind the pinch off voltage where the drain current increase rapidly is known as Ohmic Region.

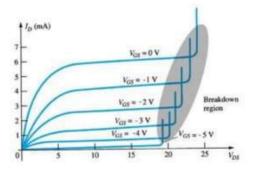

### **Break Down Region**

☐ It is the region, when the drain-source voltage (VDS) is high enough to cause the JFET's resistive channel to breakdown and pass uncontrolled maximum current.

## **Advantages**

- It is simpler to fabricate, smaller in size.

- It has longer life and higher efficiency.

- It has high input impedance.

- It has negative temperature coefficient of resistance.

- It has high power gain.

# Disadvantages

- Greater susceptibility to damage in its handling.

- JFET has low voltage gain.

- > Voltage controlled resistor

- > Analog switch or gate

- > Act as an amplifier

- > Low-noise amplifier

- Constant current source