### **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35. An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### **COURSE NAME : 23CST202 – OPERATING SYSTEMS**

#### **II YEAR/ IV SEMESTER**

#### **UNIT – III STORAGE MANAGEMENT**

**Topic: Paging**

Dr.V.Savitha

Associate Professor Department of Computer Science and Engineering

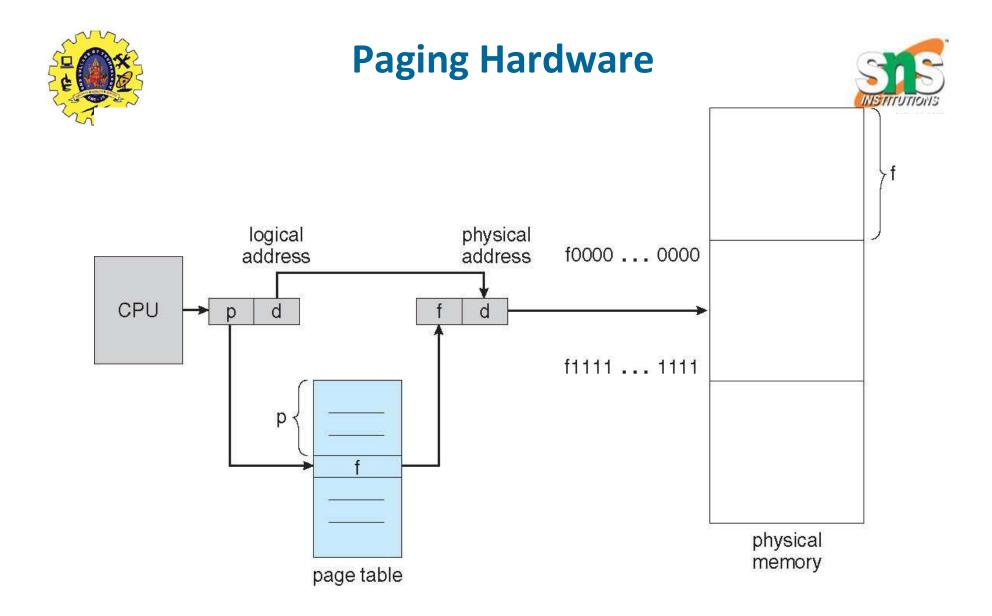

Physical address space of a process can be noncontiguous; process is allocated physical memory whenever the latter is available

- Avoids external fragmentation

- Avoids problem of varying sized memory chunks

- Divide physical memory into fixed-sized blocks called frames

- Size is power of 2, between 512 bytes and 16 Mbytes

- Divide logical memory into blocks of same size called pages

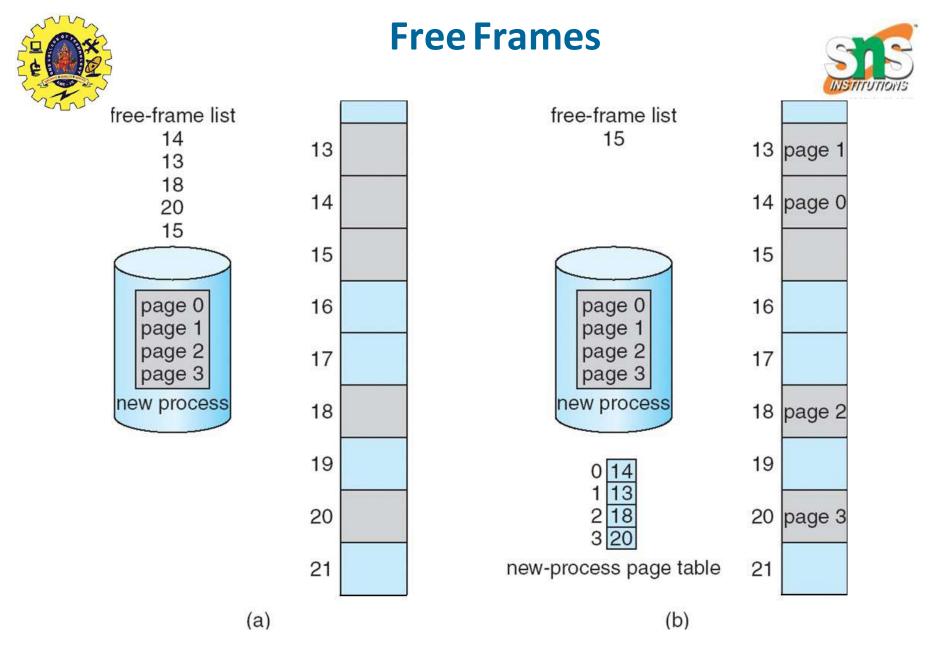

- Keep track of all free frames

- To run a program of size N pages, need to find N free frames and load program

- Set up a page table to translate logical to physical addresses

- Backing store likewise split into pages

- Still have Internal fragmentation

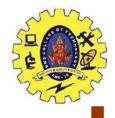

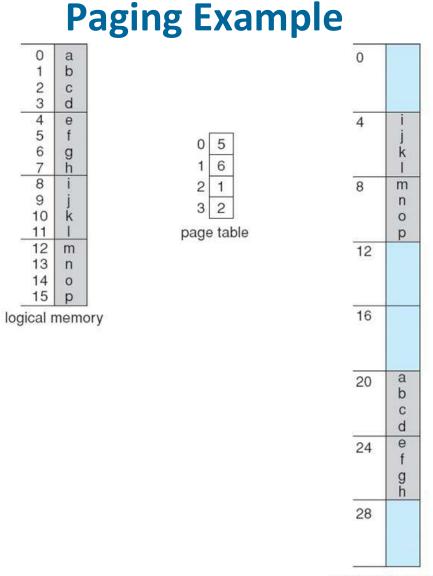

## **Address Translation Scheme**

Address generated by CPU is divided into:

- Page number (p) used as an index into a page table which contains base address of each page in physical memory

- Page offset (d) combined with base address to define the physical memory address that is sent to the memory unit

| page number | page offset |

|-------------|-------------|

| р           | d           |

| m -n        | n           |

• For given logical address space 2<sup>*m*</sup> and page size 2<sup>*n*</sup>

physical memory

#### *n*=2 and *m*=4 32-byte memory and 4-byte pages

19CSB201-Operating Systems/Dr. V.Savitha-AP/CSE

# Paging (Cont.)

- Calculating internal fragmentation

- Page size = 2,048 bytes

- Process size = 72,766 bytes

- 35 pages + 1,086 bytes

- Internal fragmentation of 2,048 1,086 = 962 bytes

- Worst case fragmentation = 1 frame 1 byte

- On average fragmentation = 1 / 2 frame size

- So small frame sizes desirable?

- But each page table entry takes memory to track

- Page sizes growing over time

- Solaris supports two page sizes 8 KB and 4 MB

- Process view and physical memory now very different

- By implementation process can only access its own memory

19CSB201-Operating Systems/Dr. V.Savitha-AP/CSE

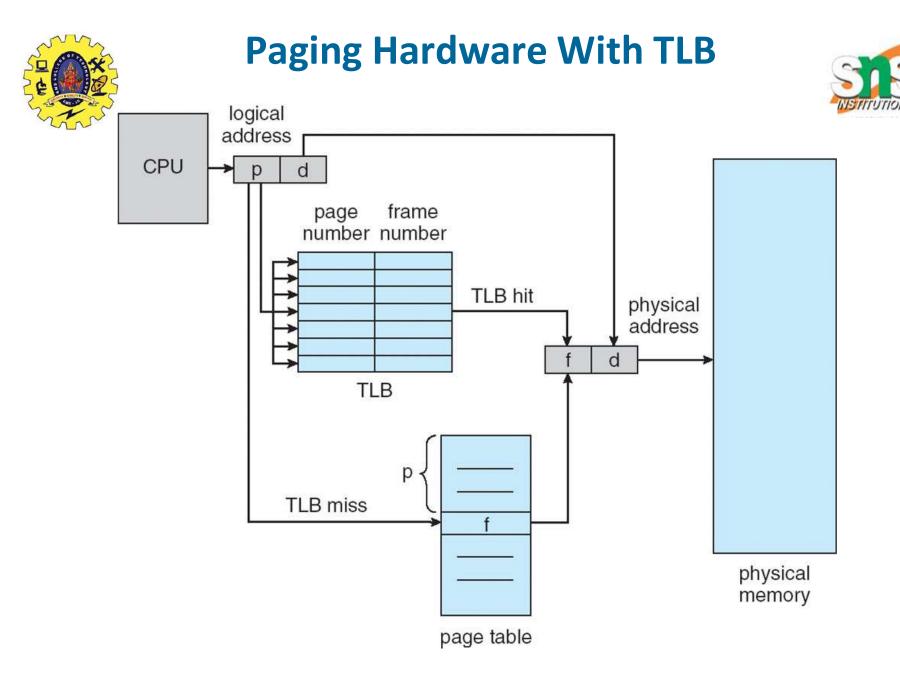

## **Implementation of Page Table**

- Page table is kept in main memory

- Page-table base register (PTBR) points to the page table

- Page-table length register (PTLR) indicates size of the page table

- In this scheme every data/instruction access requires two memory accesses

- One for the page table and one for the data / instruction

- The two memory access problem can be solved by the use of a special fast-lookup hardware cache called associative memory or translation look-aside buffers (TLBs)

## **Implementation of Page Table**

- Some TLBs store address-space identifiers (ASIDs) in each TLB entry – uniquely identifies each process to provide address-space protection for that process

- Otherwise need to flush at every context switch

- TLBs typically small (64 to 1,024 entries)

- On a TLB miss, value is loaded into the TLB for faster access next time

- Replacement policies must be considered

- Some entries can be wired down for permanent fast access

### **Associative Memory**

Associative memory – parallel search

| Page # | Frame # |

|--------|---------|

|        |         |

|        |         |

|        |         |

|        |         |

- Address translation (p, d)

- If p is in associative register, get frame # out

- Otherwise get frame # from page table in memory

### **Effective Access Time**

- Associative Lookup =  $\varepsilon$  time unit

- Can be < 10% of memory access time

- Hit ratio =  $\alpha$

- Hit ratio percentage of times that a page number is found in the associative registers; ratio related to number of associative registers

- Consider  $\alpha$  = 80%,  $\varepsilon$  = 20ns for TLB search, 100ns for memory access

- Effective Access Time (EAT)

$$EAT = (1 + \varepsilon) \alpha + (2 + \varepsilon)(1 - \alpha)$$

$$= 2 + \varepsilon - \alpha$$

Consider  $\alpha$  = 80%,  $\varepsilon$  = 20ns for TLB search, 100ns for memory access

• EAT = 0.80 x 100 + 0.20 x 200 = 120ns

- Consider more realistic hit ratio ->  $\alpha$  = 99%,  $\varepsilon$  = 20ns for TLB search, 100ns for memory access

- EAT = 0.99 x 100 + 0.01 x 200 = 101ns

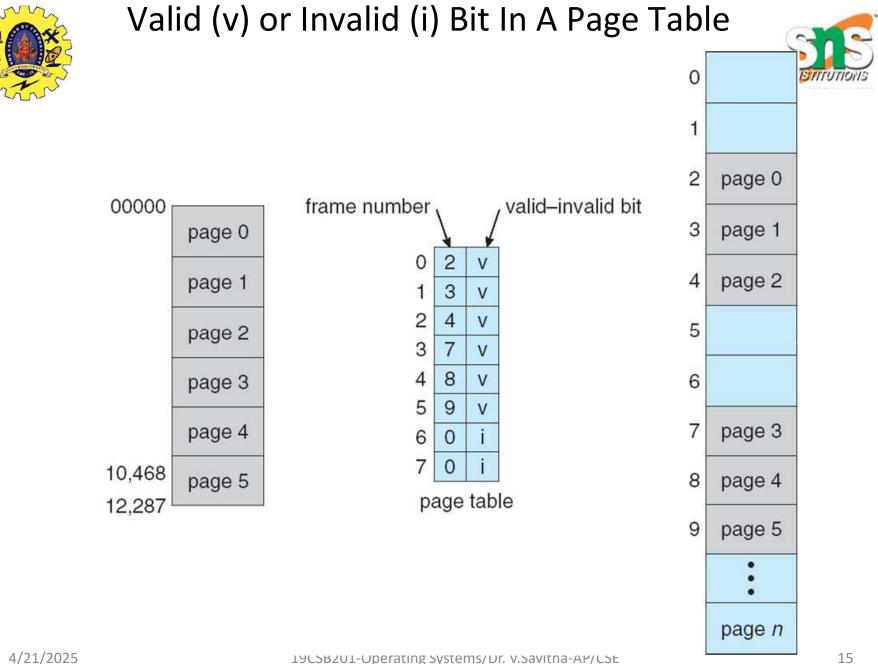

### **Memory Protection**

- Memory protection implemented by associating protection bit with each frame to indicate if read-only or read-write access is allowed

- Can also add more bits to indicate page execute-only, and so on

- **Valid-invalid** bit attached to each entry in the page table:

- "valid" indicates that the associated page is in the process' logical address space, and is thus a legal page

- "invalid" indicates that the page is not in the process' logical address space

- Or use page-table length register (PTLR)

- Any violations result in a trap to the kernel