# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

### **23ECT201-ELECTRONIC CIRCUITS**

### **UNIT 1 BJT AND FET BIASING**

### **TOPIC 1 : OPERATING POINT**

# **OPEARTING POINT**

Q-point: It is point on load line which represents DC value of V<sub>CE</sub> and I<sub>C</sub> in absence of signal. Best position is mid-point on load line, VCE= 1/2 VCC

- ▶ For transistor amplifiers the resulting dc current and voltage establish an operating point on the characteristics that define the region that will be employed for amplification of the applied signal.

- Since the operating point is a fixed point on the characteristics, it is also called the quiescent point (abbreviated Q-point).

- ▶ By definition, quiescent means quiet, still, inactive. Figure shows a general output device characteristic with four operating points indicated.

# **NEED OF OPERATING POINT**

- Temperature causes the device parameters such as the transistor current gain (ac) and the transistor leakage current (ICEO) to change.

- Higher temperatures result in increased leakage currents in the device, thereby changing the operating condition set by the biasing network. The result is that the network design must also provide a degree of *temperature stability* so that temperature changes result in minimum changes in the operating point.

- This maintenance of the operating point can be specified by a stability factor, S.

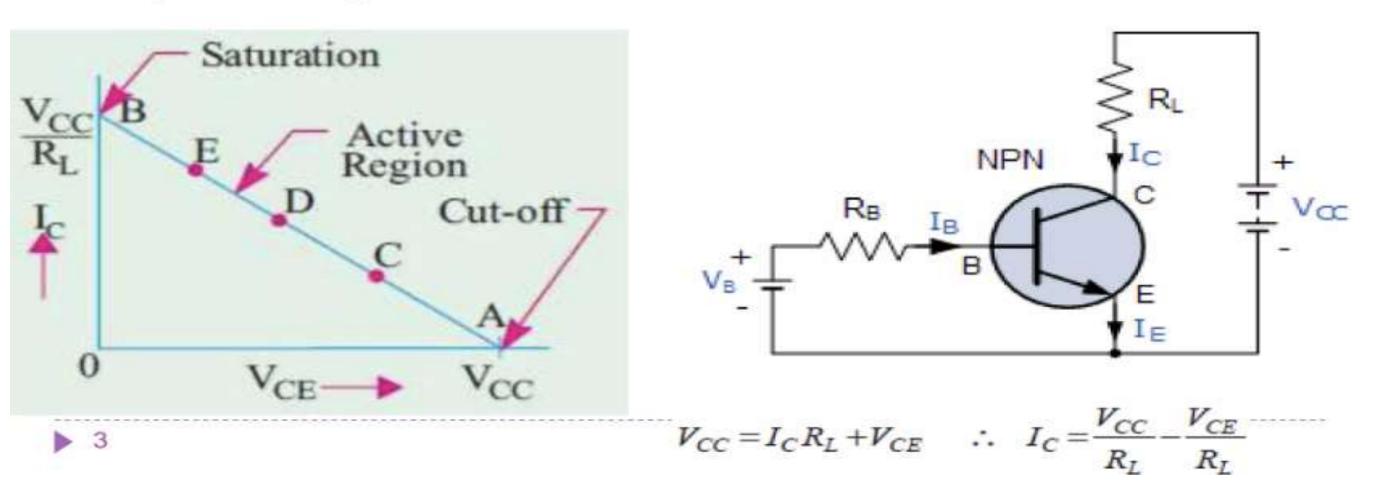

# **DC LOAD LINE**

- Load line: locus of operating point on o/p characteristics of transistor

- A line on which operating point moves according to input ac signal

**OPERATING POINT/BJT AND FET BIASING/LAKSHMI S V/ECE/SNSCT**

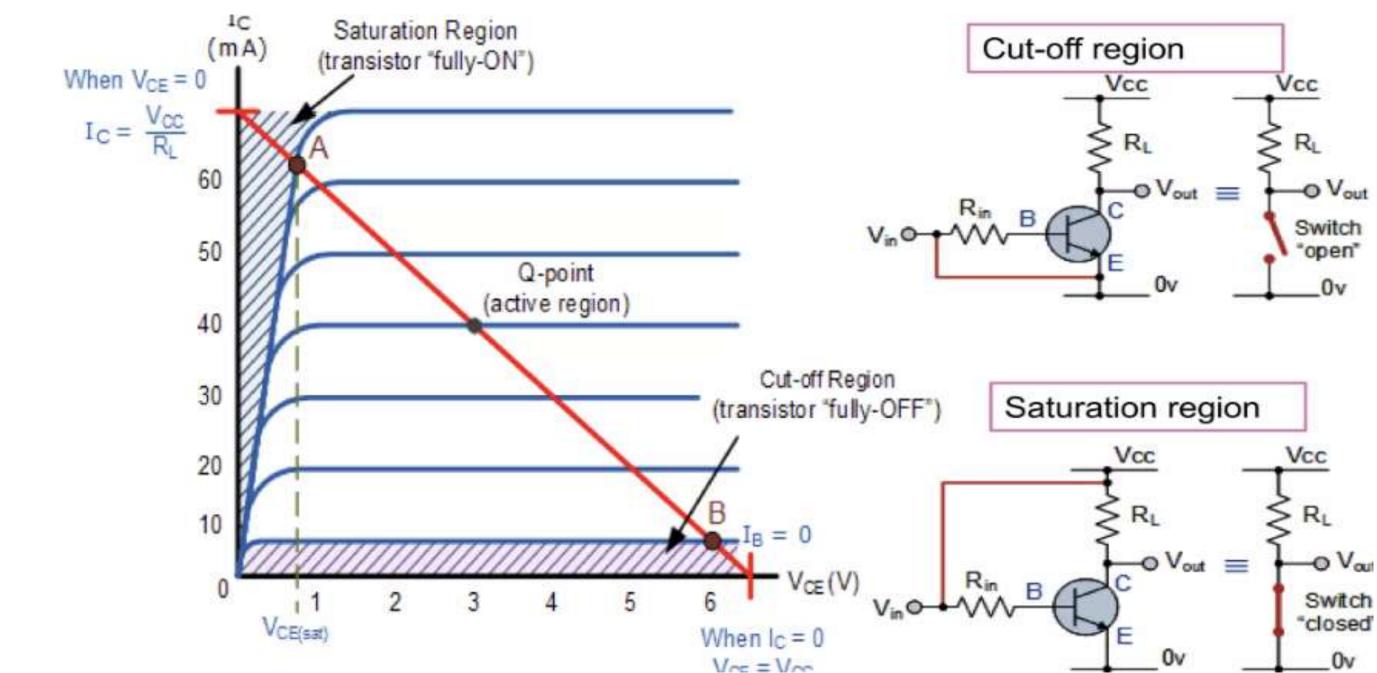

## **OPEARTING REGION**

**14/**8/2024

**OPERATING POINT/BJT AND FET BIASING/LAKSHMI S V/ECE/SNSCT**

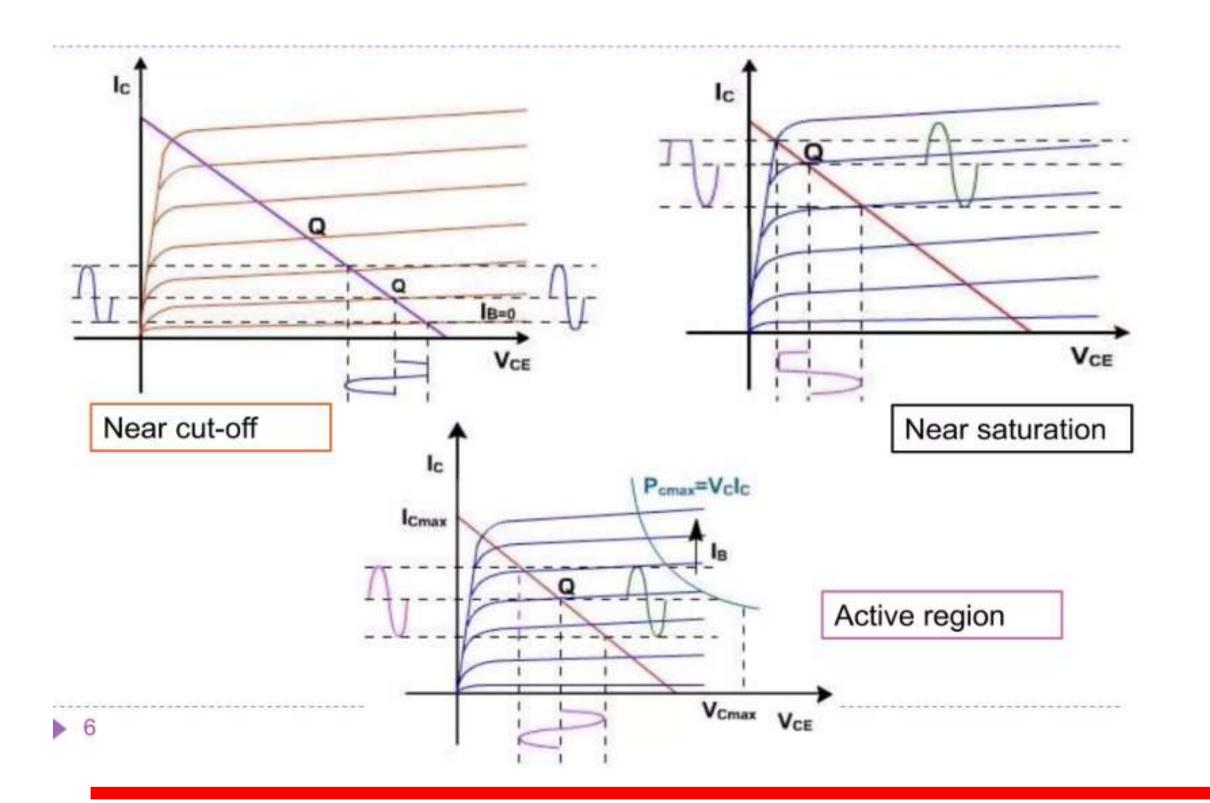

# **SELECTION OF OPERATING POINT**

**OPERATING POINT/BJT AND FET BIASING/LAKSHMI S V/ECE/SNSCT**

14/8/2024

## **EXAMPLE**

- For CE configuration Vcc = 10 v, Rc = 8k. Draw DC 1. load line. Find Q-point for zero signal if base current is  $15\mu A$ ,  $\beta = 40$

- Ic = 1.25mA,

- > Zero signal Ic= $\beta$  I<sub>B</sub> = 0.6mA, VCE = 5.2v

- 2. In transistor ckt Rc= 5k, quiescent current is 1.2mA. Determine Q-point when Vcc=12 v. how will point change when Rc is changed from 5k to 7.5k

- Operating pt 1: (6 v, 1.2mA)

- Operating pt 2: (3 v, 1.2mA)

### Assessment

Define opearting Point

Q-point: It is point on load line which represents DC value of V<sub>CE</sub> and I<sub>C</sub> in absence of signal. Best position is mid-point on load line, V<sub>CE</sub>= 1/2 VCC

**14/**8/2024

OPERATING POINT/BJT AND FET BIASING/LAKSHMI S V/ECE/SNSCT

13**/13**