# SNS COLLEGE OF TECHNOLOGY

(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

#### Topic 1.7 : Biasing the FET & Fixed Bias configuration

Design of binning for JEET \* FET - Field Ettert Transistor - It's a semiconductor device which depends for its operation on the control of current by an electric Junction field Effect Metal-onide-semi conductor Transistor (or) FFT Transistor (MOSFET) FET differs from the BIT in the following characteristics 1. It's operation depends upon the flow of majority camers Only. 2. It's simpler to fabricate 4 occupies less space. 3. It enhibits a high input resistance, typically many megaohous. 4. It's less hoisy compared to BJT. 5. It exhibits no offset voll-age at zuro drain current Disadvantages of FET \* Small gain bandwidth product. Symbol: p-channel h + channel \* The general relationship that can be applied to the de analysis of all FET amplifiers are I to = 0 Amps ID = Is $Ip = Ipss \left(1 - \frac{Vas}{Vp}\right)^2$

# SNS COLLEGE OF TECHNOLOGY

(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

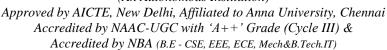

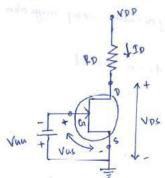

### 1. Fined Bias | Grate Bias

\* To make the habe-source junction reverthe biand a separate supply voior is connected such that gate is more negative than the source.

#### De Analysis:

\* For de analysis coupling capacitors are open circuited.

\* The current Through Ron is Ion which is D.

\* This permits Ru to replace by short circuit

equivalent, simplifying the fined bias circuit.

Ide know for de analysis

Ici = 0 amps

Apply KVL to the Grate to source junction

\* Since Van is a fined de supply. The voltage Vus is fixed in magnitude 4 hence The name fixed bias circuit

\* For fined bias circuit The ID can be calculated as

\* Apply KVI to The Drain to Source junction

Q-point