#### **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

#### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

#### 23ECB221 – DIGITAL ELECTRONICS

Decade Counter/ 23ECB221/ DIGITAL ELECTRONICS/P.UMA MAHESWARI/AP/ECE/SNSCT II YEAR/ III SEMESTER

UNIT 3 – SEQUENTIAL CIRCUITS

**TOPIC** -Decade Counter

#### **DE CADE COUNTER**

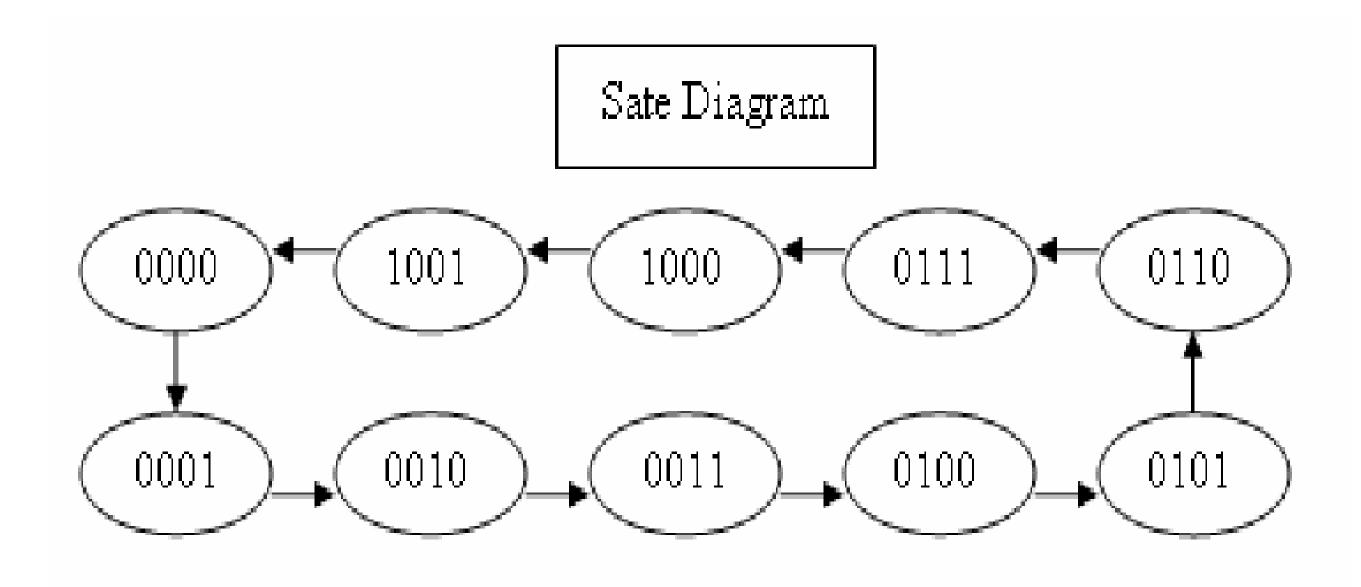

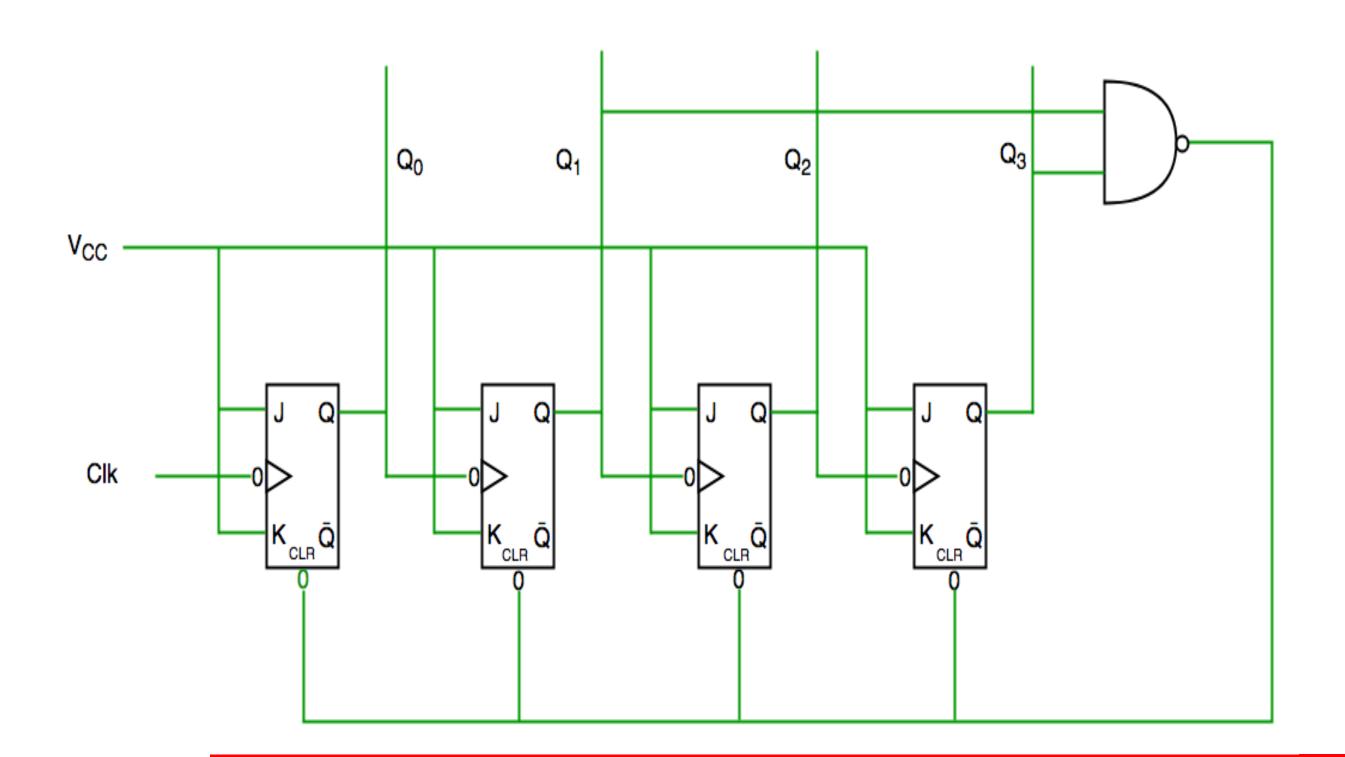

A decade counter is a binary counter that is designed to count to 1010 (decimal 10). An ordinary four-stage counter can be easily modified to a decade counter by adding a NAND gate as in the schematic to the right. ... The NAND gate outputs are connected to the CLR input of each of the FFs.

#### **DE CADE COUNTER**

## **Decade Counter Truth Table**

| Clock |    | Decima |              |    |       |  |

|-------|----|--------|--------------|----|-------|--|

| Count | QD | QC     | QB           | QA | Value |  |

| 1     | 0  | 0      | 0            | 0  | 0     |  |

| 2     | 0  | 0      | 0            | 1  | 1     |  |

| 3     | 0  | 0      | 1            | 0  | 2     |  |

| 4     | 0  | 0      | ĭ            | 1  | 3     |  |

| 5     | 0  | 1      | 0            | 0  | 4     |  |

| 6     | 0  | 1      | 0            | 1  | 5     |  |

| 7     | 0  | 1      | 1            | 0  | 6     |  |

| 8     | 0  | 1      | 1            | 1  | 7     |  |

| 9     | 1  | 0      | 0            | 0  | 8     |  |

| 10    | 1  | 0      | 0            | 1  | 9     |  |

| 11    | -  |        | ets its Outp |    | 7     |  |

## **Logical Diagram**

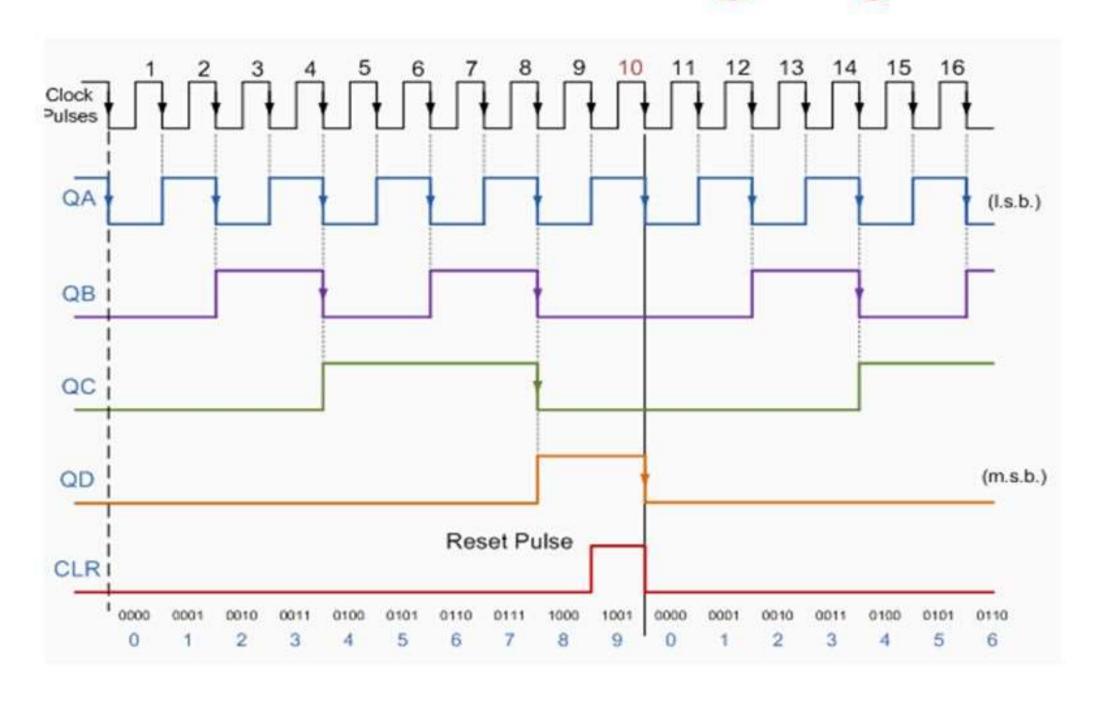

## Decade Counter Timing Diagram

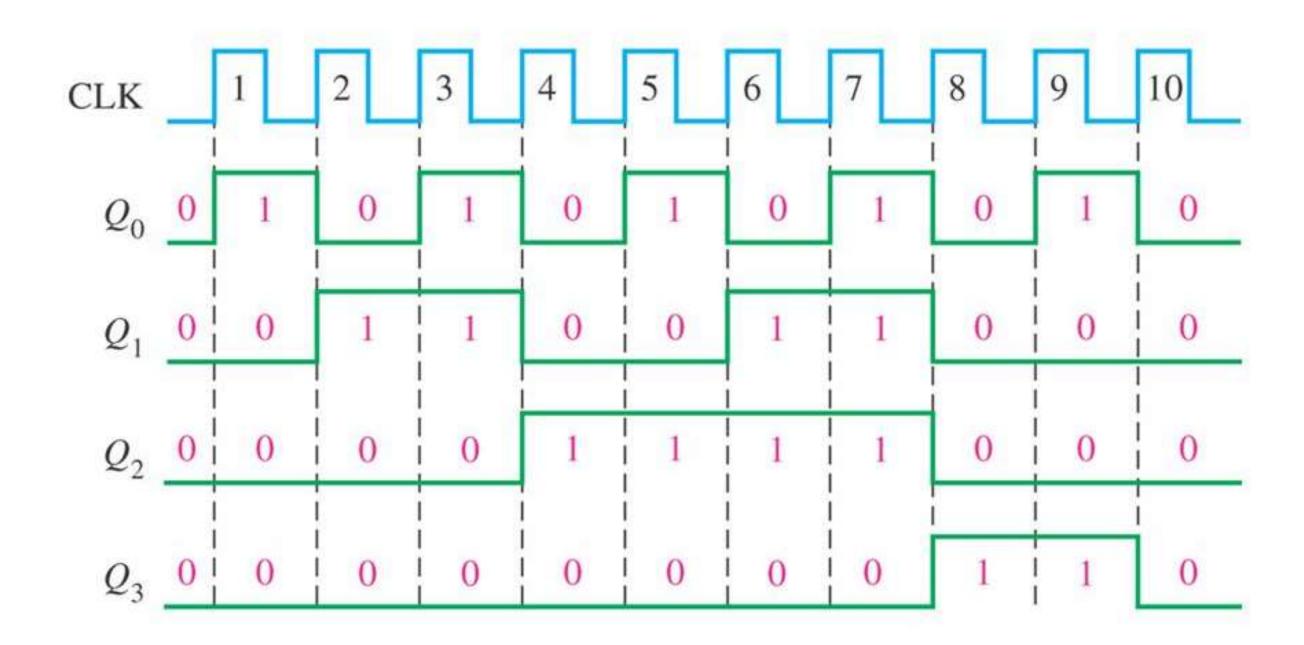

## Design Synchronous Decade Counter Using T flip flop

#### **Excitation table**

| Present State |              |      |      | Next State       |        |        |        | Flip-flop Inputs |         |      |    |

|---------------|--------------|------|------|------------------|--------|--------|--------|------------------|---------|------|----|

| QD            | Qc           | QB   | QA   | Q <sub>D+1</sub> | QC + 1 | QB + 1 | QA + 1 | TD               | TC      | TB   | TA |

| 0             | 0            | 0    | 0    | 0                | 0      | 0      | 1      | 0                | 0       | 0    | 1  |

| 0             | 0            | 0    | 1    | 0                | 0      | 1      | 0      | 0                | 0       | 1    | 1  |

| 0             | 0            | 1    | 0    | 0                | 0      | 1      | 1      | 0                | 0       | 0    | 1  |

| 0             | 0            | 1    | 1    | 0                | 1      | 0      | 0.     | 0                | - 1     | - 11 | 1  |

| 0             | 1 :          | 35.0 | 0    | 0                | 1 = 1  | 0      | 1      | 0                | , ≥ 0 ≥ | 0 ,  | 1  |

| 0             | - 1          | 0    | - 1  | 0                | 1.     | . 1    | 0      | 0                | 0 -     | 1    | 1  |

| 0             | 1 .          | 1    | 0    | 0                | 1      | 71     | 1      | 0                | 0       | 0    | 1  |

| 0             | r - <b>1</b> | 1-1- | 1    | 1                | 0      | 0      | 0      | 11               |         | -1   | 1  |

| 1             | 0            | . 0  | 0    | 1                | 0      | 0      | 1      | 0                | 0       | 0    | 1  |

| 1             | 0 3          | - 0  | 1    | 0                | -0,0   | e 0    | 0      | 1 5              | 0       | 0    | 1  |

| 1             | 0            | 1    | 0    | х                | х      | ×      | х      | х                | x       | х    | х  |

| 1             | 0 =          | 101  | 1    | х                | XTV    | : x    | х      | х                | - X -   | X    | х  |

| 1             | 1.1          | 0    | 0    | х                | X-     | X      | ×      | X                | X -     | × /  | X  |

| 1             | /1           | 0    | 11   | X                | X      | X      | х      | Χ                | X       | X.   | X  |

| 1             | 1            | 1    | 0    | x                | X      | X      | X      | X                | X       | х    | X  |

| 1             | -            | 1    | -i 1 | X                | - x    | ×      | х      | X                | ×       | ×    | x  |

## Design Synchronous Decade Counter Using T flip flop

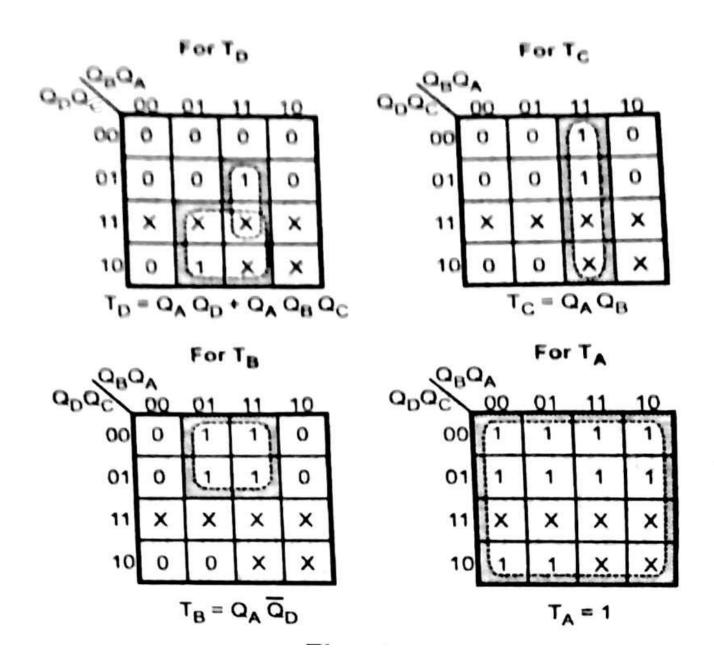

#### K-map simplification

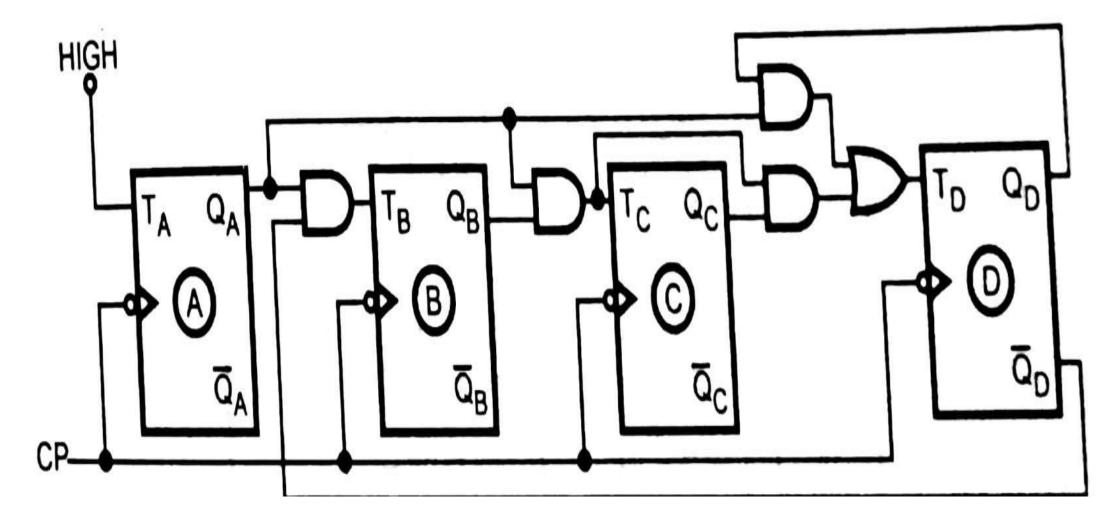

## Design Synchronous Decade Counter Using T flip flop

# Logic Diagram

#### **ASSESSMENTS**

- 1.What is BCD Counter?

- 2.Design synchronous decade counter using T flip flop.

- 3. Difference between synchronous and Asynchronous counter.

## THANK YOU