# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

# **19ECB302–VLSI DESIGN**

III YEAR/ V SEMESTER

UNIT 3 – SEQUENTIAL LOGIC CIRCUITS

**TOPIC 3 – TIMING ISSUES**

TIMING ISSUES /19ECB302-VLSI DESIGN/M.PRADEEPA/AP/ECE/SNSCT

### OUTLINE

- SYNCHRONOUS TIMING

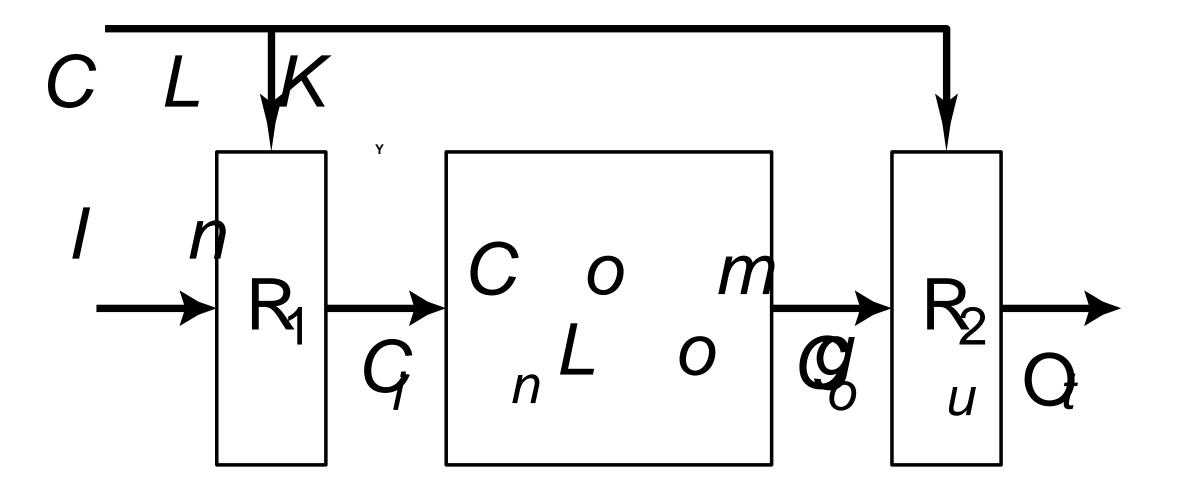

- LATCH PARAMETERS

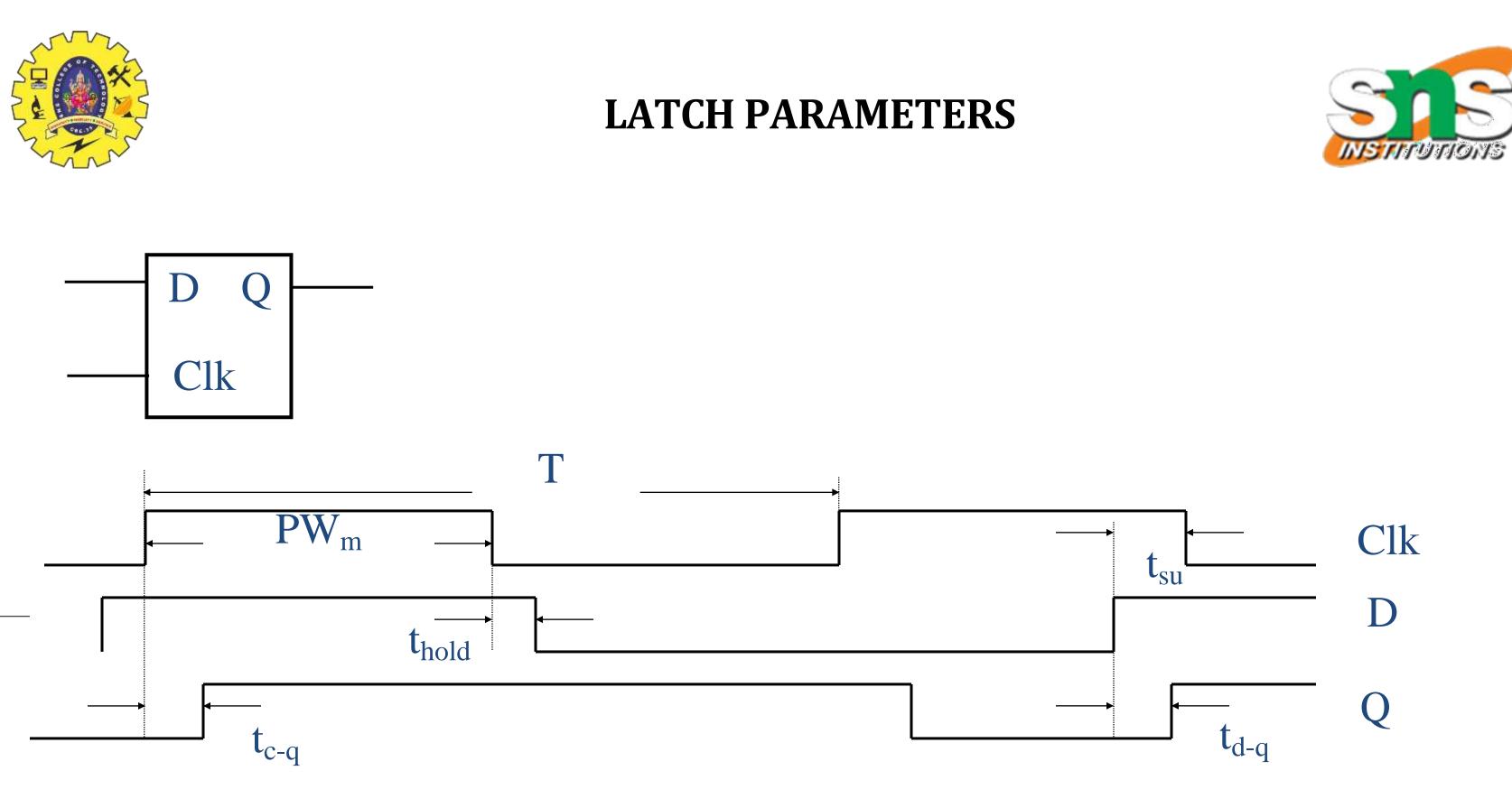

- REGISTER PARAMETERS

- CLOCK UNCERTAINTIES

- CLOCK NONIDEALITIES

- CLOCK SKEW AND JITTER

- POSITIVE AND NEGATIVE SKEW

- TIMING CONSTRAINTS

- ACTIVITY

- IMPACT OF JITTER

- SHORTEST PATH

- HOW TO COUNTER CLOCK SKEW?

- LATCH TIMING

- ASSESSMENT

- SUMMARY & THANKYOU

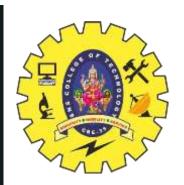

**SYNCHRONOUS TIMING**

# Delays can be different for rising and falling data transitions

19/9/2024

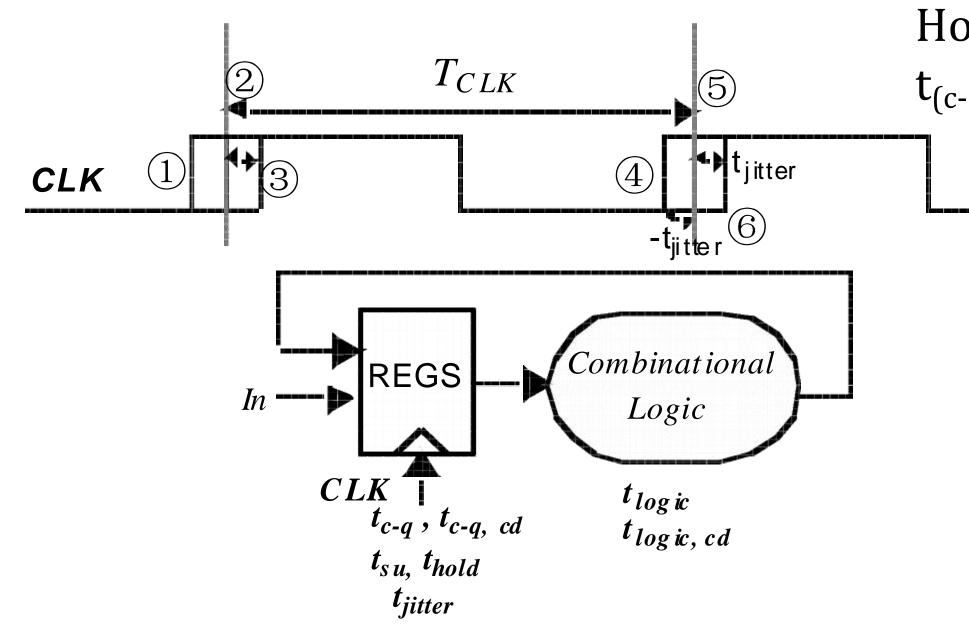

**CLOCK UNCERTAINTIES**

19/9/2024<sup>2024</sup>

TIMING ISSUES /19ECB302-VLSI DESIGN MPRADEEPAAAPFEEEFS SISSOT

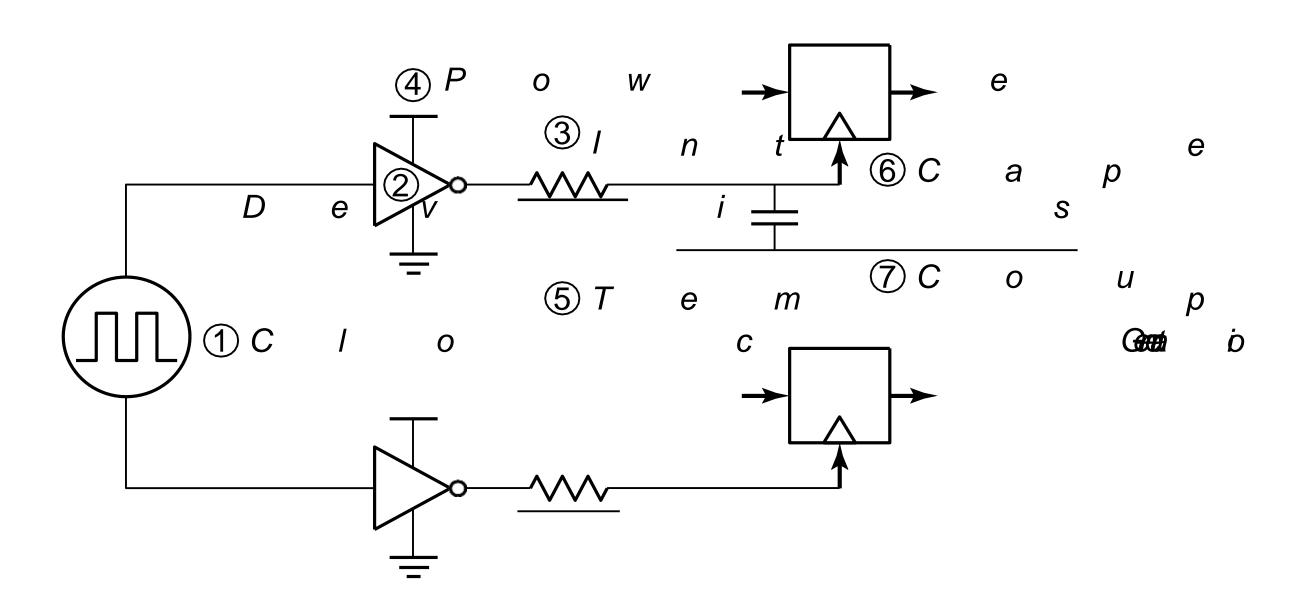

# **CLOCK NONIDEALITIES**

# Clock skew

-Spatial variation in temporally equivalent clock edges; deterministic + random, *t<sub>SK</sub>*

# Clock jitter

- -Temporal variations in consecutive edges of the clock signal; modulation + random noise

- -Cycle-to-cycle (short-term)  $t_{IS}$

- -Long term  $t_{IL}$

# Variation of the pulse width

–Important for level sensitive clocking

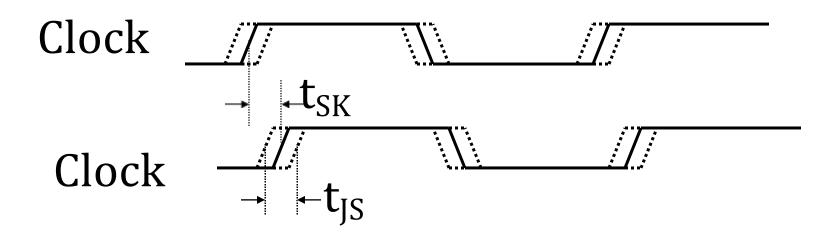

**CLOCK SKEW AND JITTER**

- Both skew and jitter affect the effective cycle time

- Only skew affects the race margin

19/9/2024

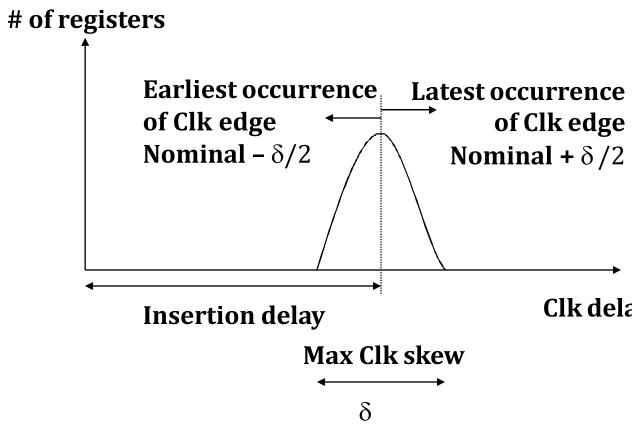

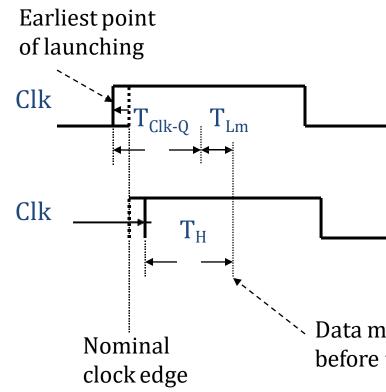

#### **CLOCK SKEW**

of Clk edge

Clk delay

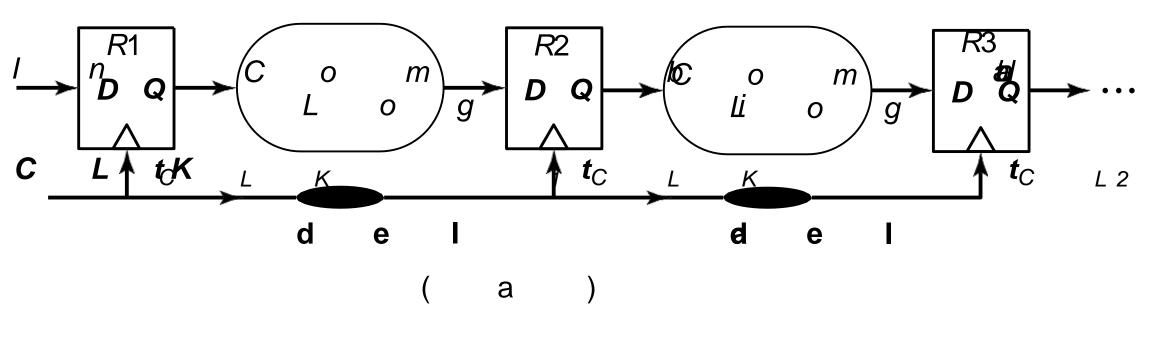

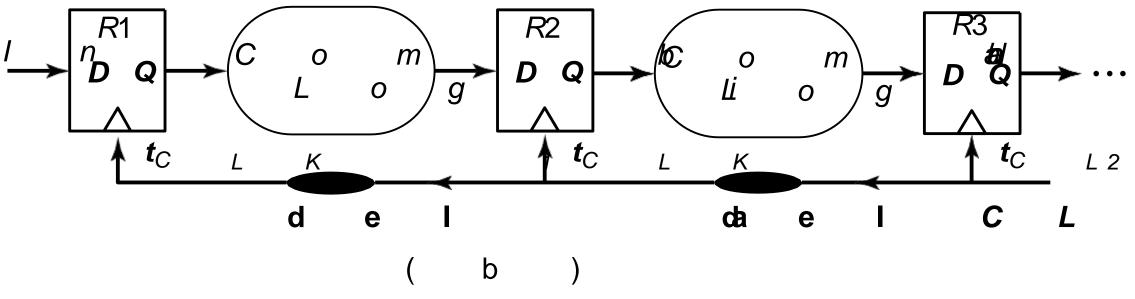

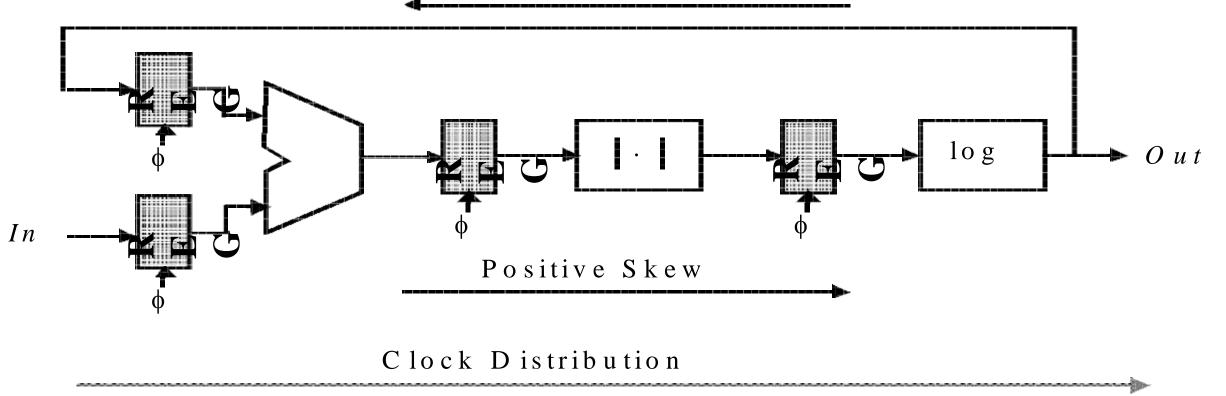

#### **POSITIVE AND NEGATIVE SKEW**

TIMING ISSUES /19ECB302-VLSI DESIGNM.PRADEEPA/AP/ECE/SNSCT

### **POSITIVE SKEW & NEGATIVE SKEW**

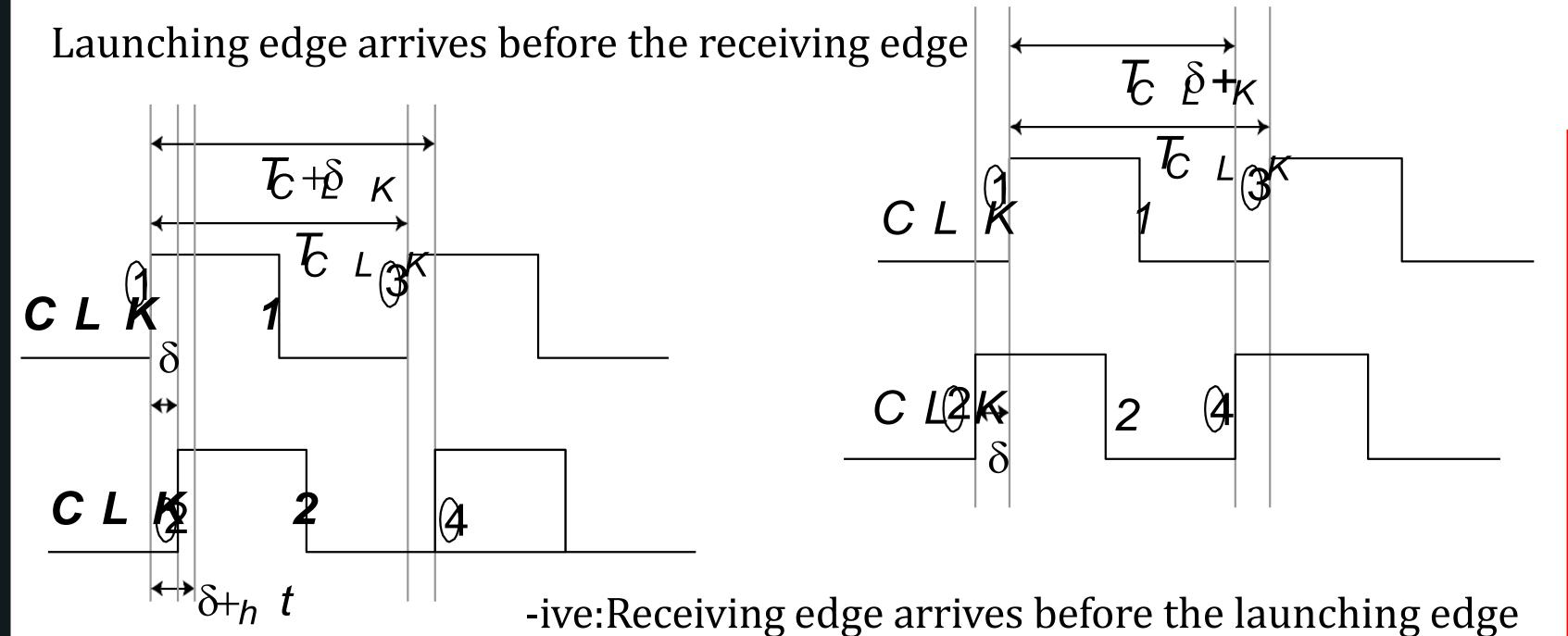

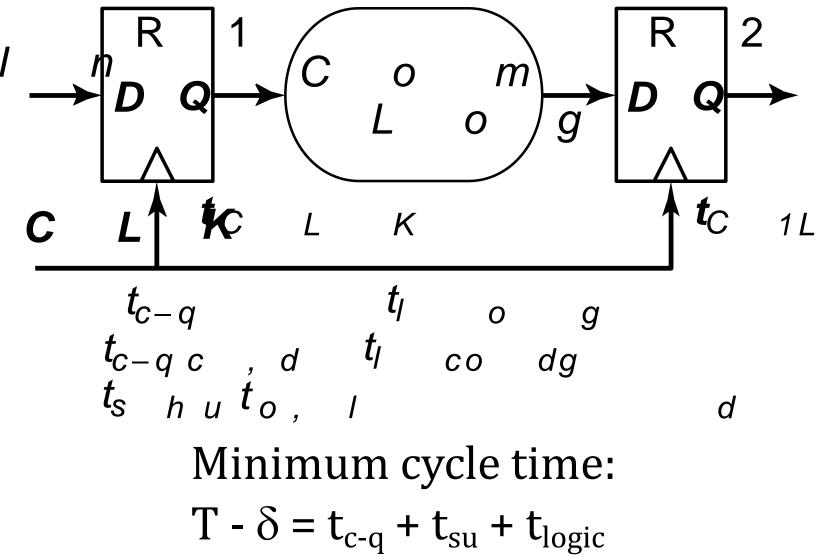

#### **TIMING CONSTRAINTS**

Worst case is when receiving edge arrives early (positive  $\delta$ )

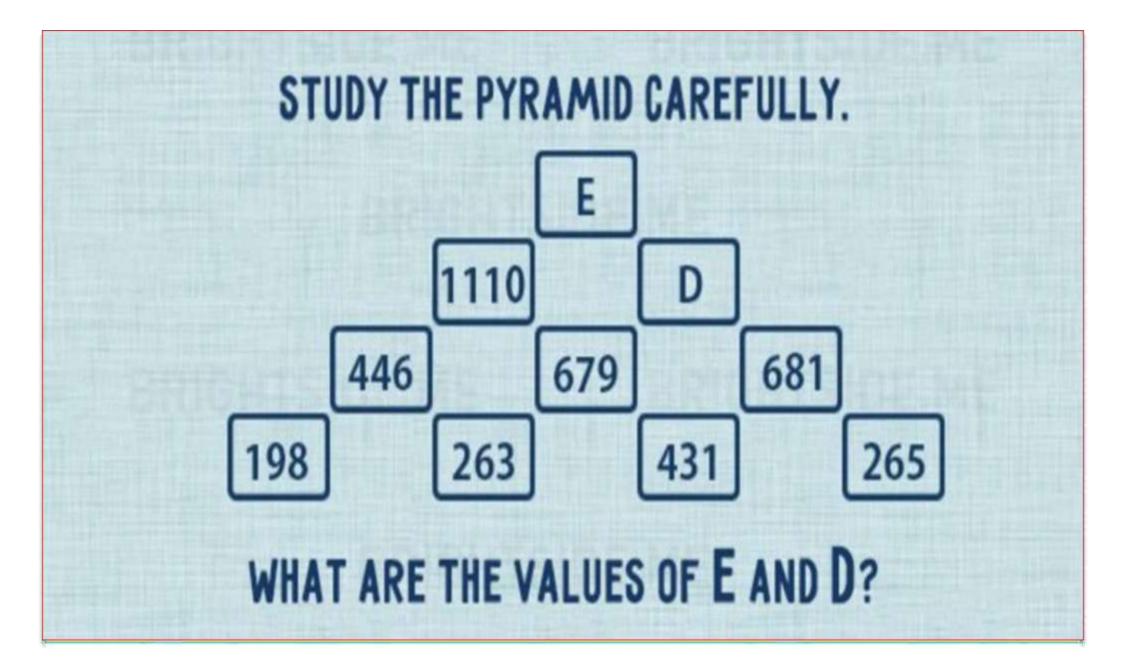

### **CLASS ROOM ACTIVITY**

TIMING ISSUES /19ECB302-VLSI DESIGNM.PRADEEPA/AP/ECE/SNSCT

**IMPACT OF JITTER**

# Hold time constraint: $t_{(c-q, cd)} + t_{(logic, cd)} > t_{hold} + \delta$

# **SHORTEST PATH**

# Worst case is when receiving edge arrives late Race between data and clock

TIMING ISSUES /19ECB302-VLSI DESIGNM.PRADEEPA/AP/ECE/SNSCT

19/9/2024

Data must not arrive before this time

### **HOW TO COUNTER CLOCK SKEW?**

Negative Skew

Data and Clock Routing

TIMING ISSUES /19ECB302-VLSI DESIGNM.PRADEEPA/AP/ECE/SNSCT

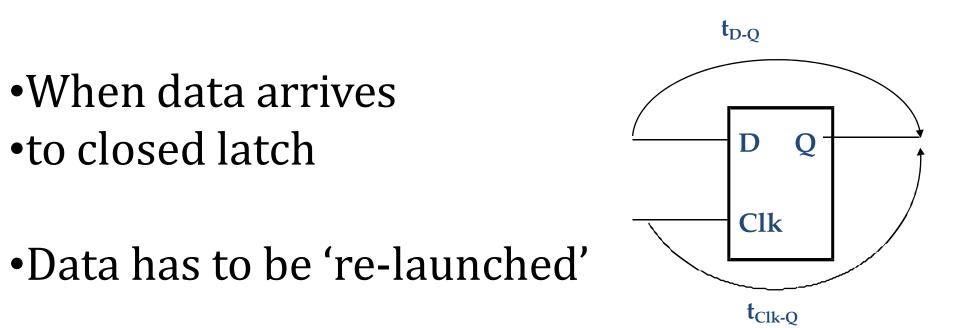

#### LATCH TIMING

#### •Latch is a 'soft' barrier

19/9/2024

TIMING ISSUES /19ECB302-VLSI DESIGNM.PRADEEPA/AP/ECE/SNSCT

### •When data arrives to transparent latch

### ASSESSMENT

- 1. Compare latch & Register parameters

- 2. Define Clock Skew & Jitter

- 3. Differentiate positive skew & negative skew

- 4. How to counter clock skew?

# **SUMMARY & THANK YOU**

19/9/2024