## **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## **19ECB302–VLSI DESIGN**

#### III YEAR/ V SEMESTER

## UNIT 3 – SEQUENTIAL LOGIC CIRCUITS

## **TOPIC 7–LOW POWER MEMORY CIRCUITS**

LOW POWER MEMORY CIRCUITS/19ECB302-VLSI DESIGN/M.PRADEEPA/AP/ECE/SNSCT

19/9/2024

## OUTLINE

- MEMORY CLASSIFICATION & MEMORY ARRAYS

- ARRAY ARCHITECTURE

- RAM VS ROM

- DRAM VS SRAM

- 6T SRAM CELL

- SRAM SIZING

- CAMS-CAM IN CACHE MEMORY, 10T CAM Cell, CAM CELL OPERATION

- ACTIVITY

- ROM

- MOS NAND ROM

- ROM EXAMPLE

- NON-VOLATILE MEMORIES THE FLOATING-GATE TRANSISTOR (FAMOS)

- PERIPHERY

- DECODERS

- SENSE AMPLIFIERS

- INPUT/OUTPUT BUFFERS

- CONTROL / TIMING CIRCUITRY

- ASSESSMENT

- SUMMARY

19/9/2024

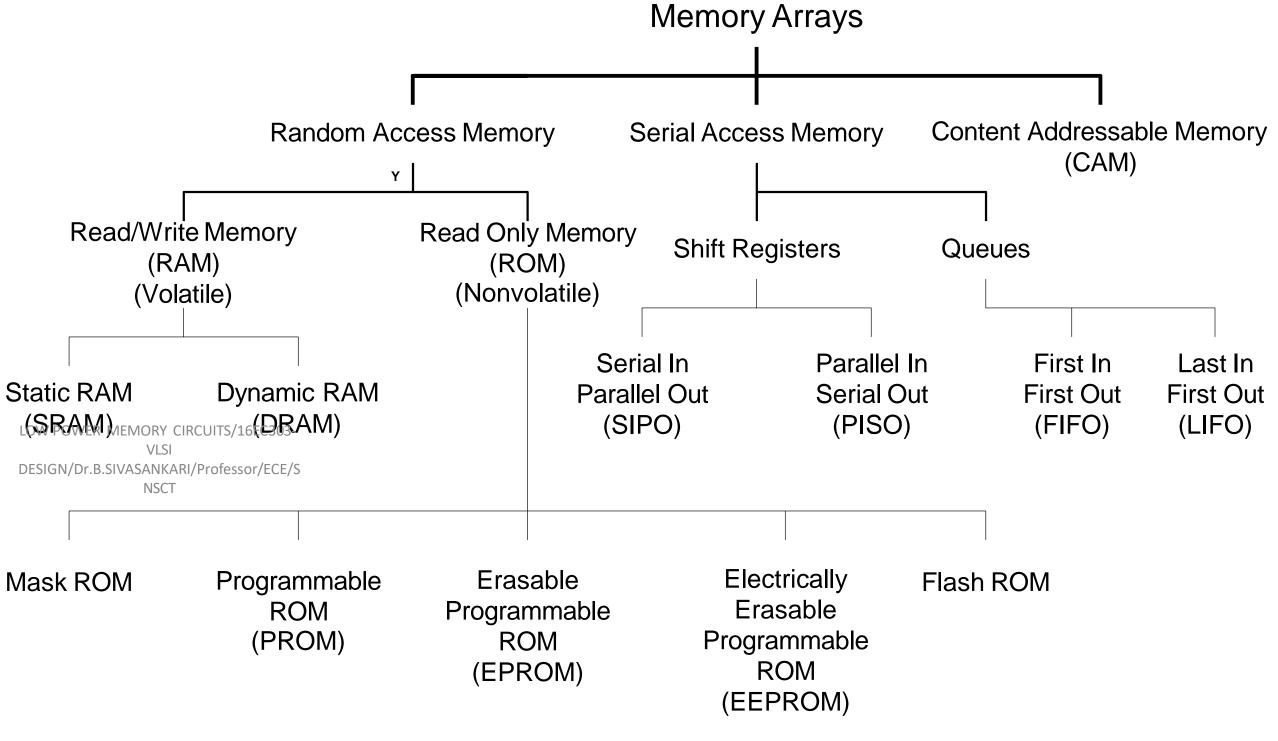

## **MEMORY ARRAYS**

## **MEMORY CLASSIFICATION**

| Read-Write Memory |                                       | Non-Volatile<br>Read-Write<br>Memory | Read-Onl |

|-------------------|---------------------------------------|--------------------------------------|----------|

| Random<br>Access  | Non-Random<br>Access                  | EPROM<br>E <sup>2</sup> PROM         | Mask-P   |

| SRAM<br>DRAM      | FIFO<br>LIFO<br>Shift Register<br>CAM | FLASH                                | Programm |

## **ARRAY ARCHITECTURE**

- 2<sup>n</sup> words of 2<sup>m</sup> bits each

- If n >> m, fold by 2<sup>k</sup> into fewer *rows* of more *columns*

- Good regularity easy to design

- Very high density if good cells are used

## **RAM VS ROM**

#### RAM

•Random write and read operation for any cell •Volatile data •Most of computer memory •DRAM •Low Cost •High Density •Medium Speed •SRAM •High Speed

- •Ease of use

- •Medium Cost

- Non-volatile Data

- Method of Data Writing

- Mask ROM

- Data written during chip fabrication

- PROM

- Fuse ROM: Non-rewritable Erase data by UV rays

- EPROM: – EEPROM: Erase and write through electrical

- means

- Speed 2-3 times slower than RAM • Upper limit on write operations • Flash Memory – High density, Low Cost

#### ROM

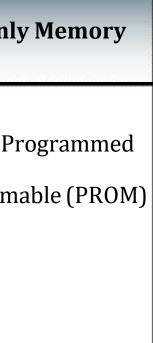

## **DRAM VS SRAM**

### DRAM

#### SRAM

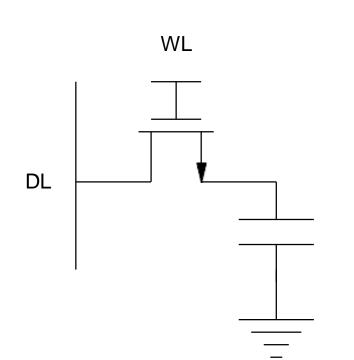

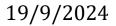

## **6T SRAM CELL**

- Cell size accounts for most of array size - Reduce cell size at expense of complexity

- 6T SRAM Cell

- Used in most commercial chips

- Data stored in cross-coupled inverters

- Read:

- Precharge bit, bit\_b

- Raise wordline

- Write:

- Drive data onto bit, bit\_b

- Raise wordline

word

bit

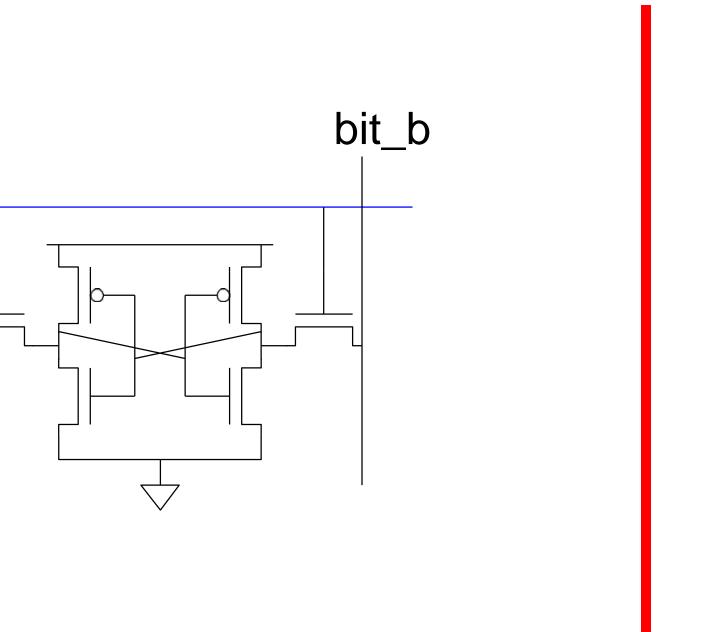

## **SRAM SIZING**

- High bitlines must not overpower inverters during reads

- But low bitlines must write new value into cell

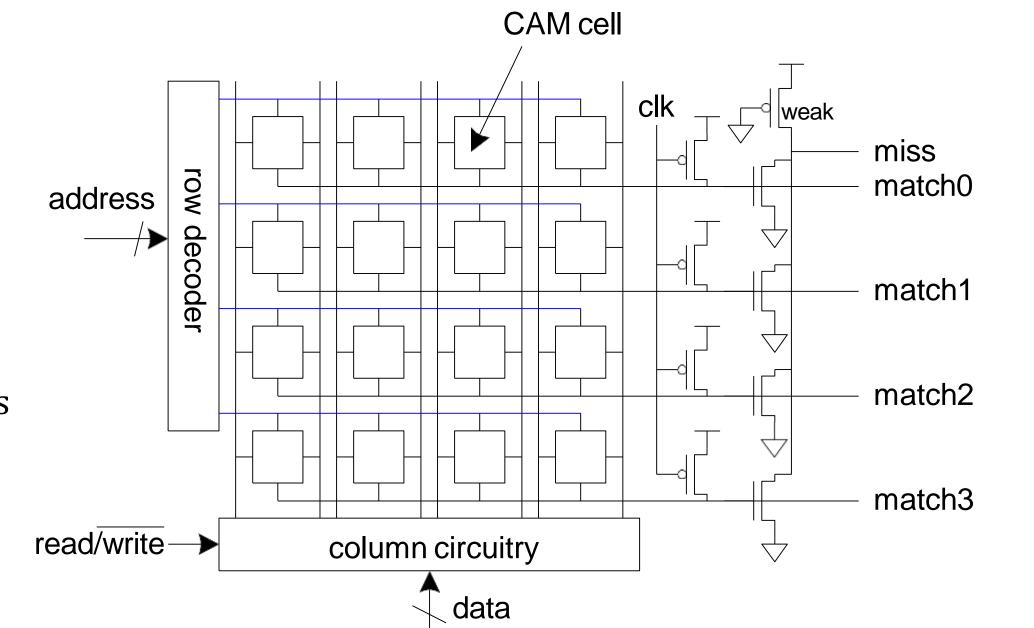

Extension of ordinary memory (e.g. SRAM) Read and write memory as usual Also match to see which words contain a key

#### Bit Bit Bit Bit Word adr data/key CAM read match CAM Word write – $\rightarrow$ ••• Wired-NOR Match Line

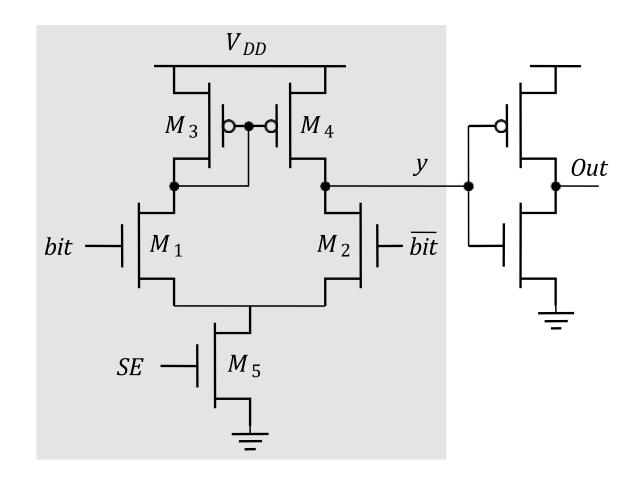

#### Static CAM Memory Cell

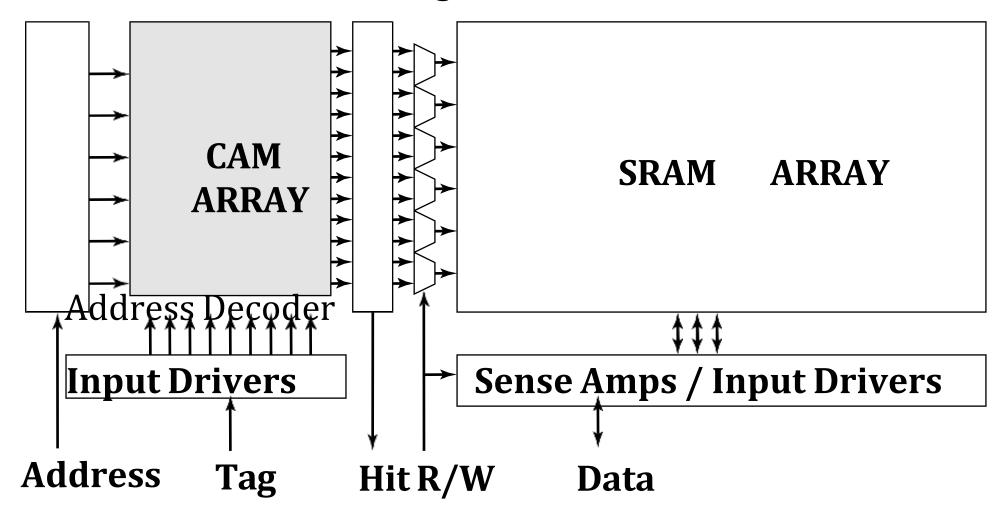

## **CAM IN CACHE MEMORY**

Hit Logic

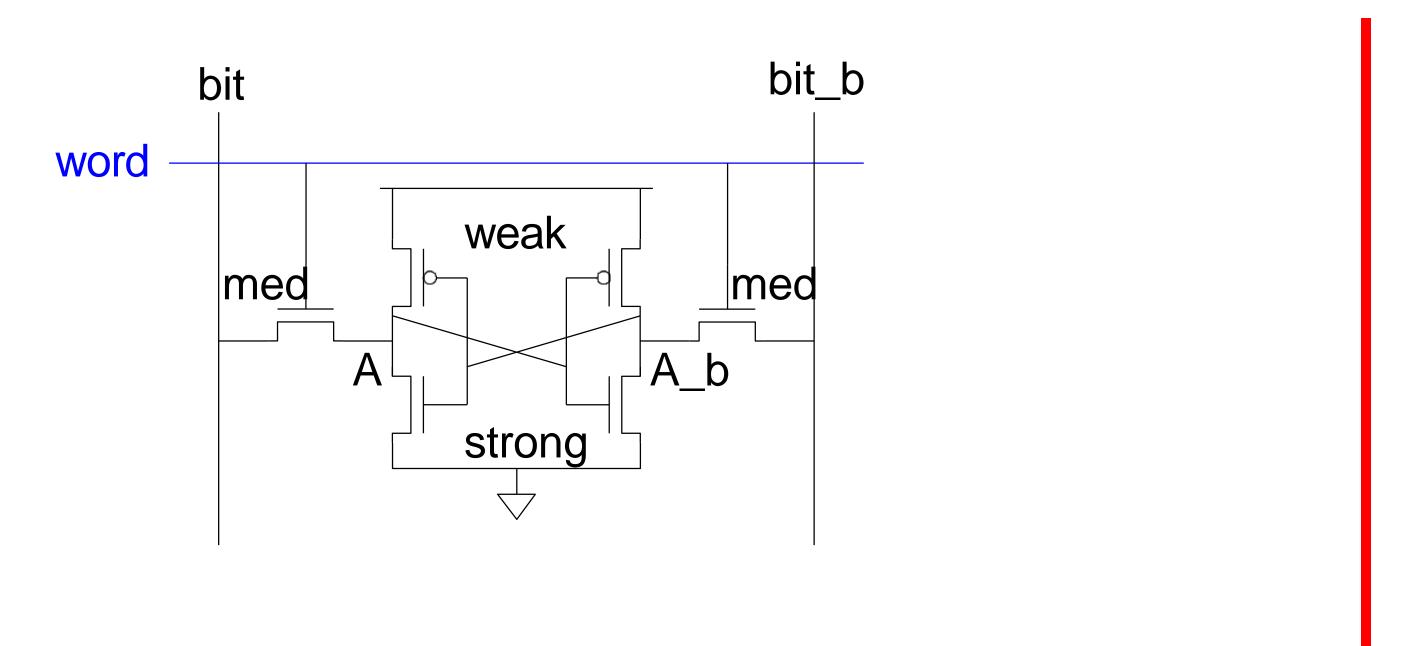

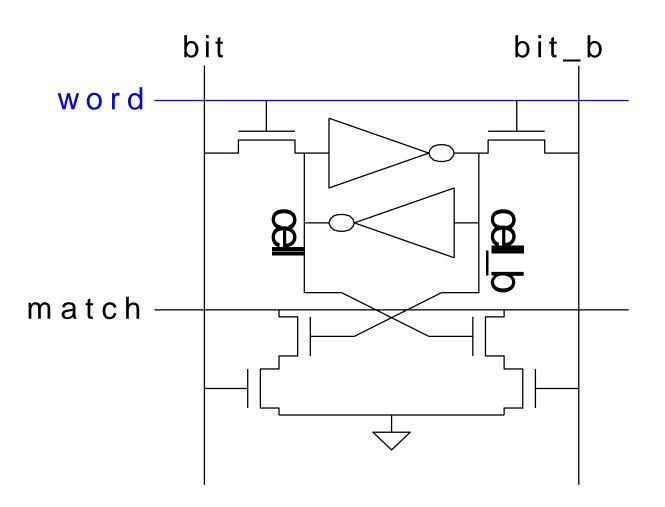

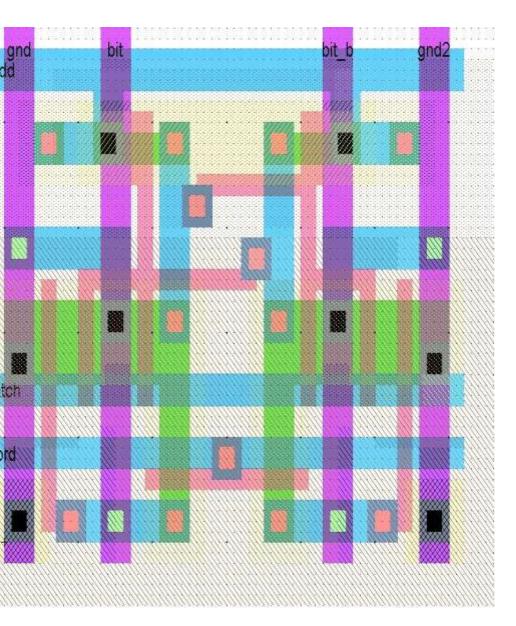

## **10T CAM Cell**

#### Add four match transistors to 6T SRAM 56 x 43 l unit cell

## **CAM CELL OPERATION**

- Read and write like ordinary SRAM

- For matching:

- Leave wordline low

- Precharge matchlines

- Place key on bitlines

- Matchlines evaluate

- Miss line

- Pseudo-nMOS NOR of match lines

- Goes high if no words match

## ROM

- •To store constants, control information and program instructions in digital systems.

- •To provide a fixed, specified binary output for every binary input.

- •simple combinational Boolean network, which produces a specified output value for each input combination, i.e. for each address.

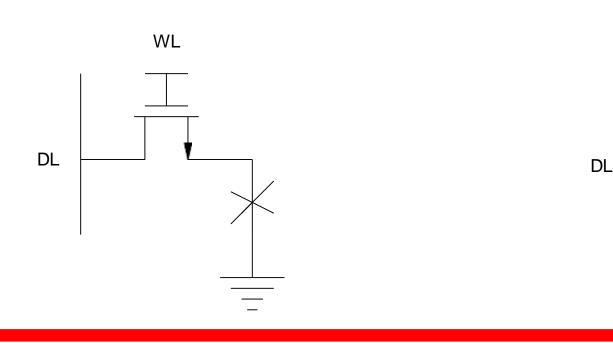

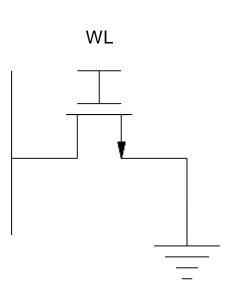

- storing binary information at a particular address location can be achieved by the presence or absence of a data path from the selected row (word line) to the selected column (bit line), which is equivalent to the presence or absence of a device at that particular location.

• Fuse ROM

19/9/2024

**EEPROM**

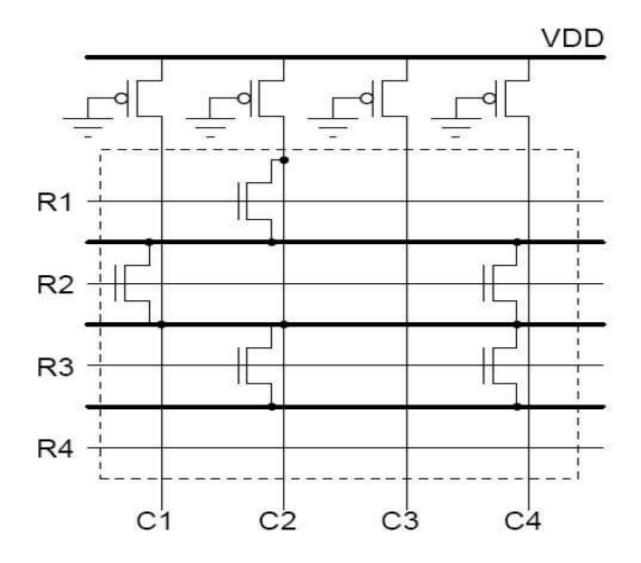

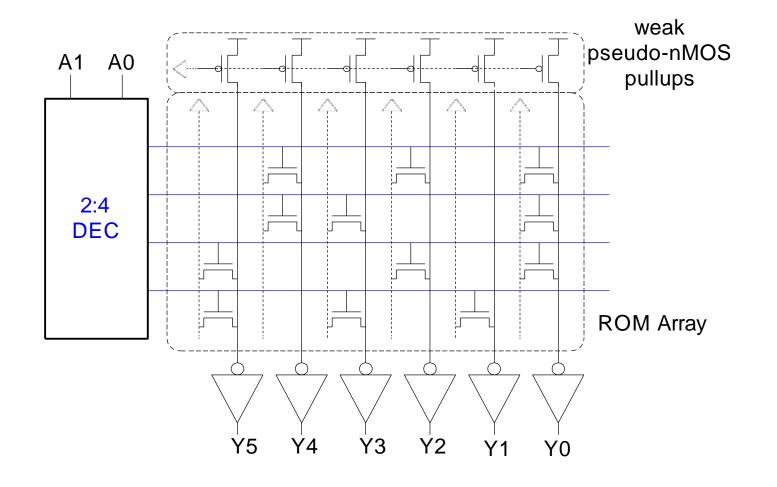

## **NAND-based ROM Array**

#### All word lines high by default with exception of selected row

19/9/2024

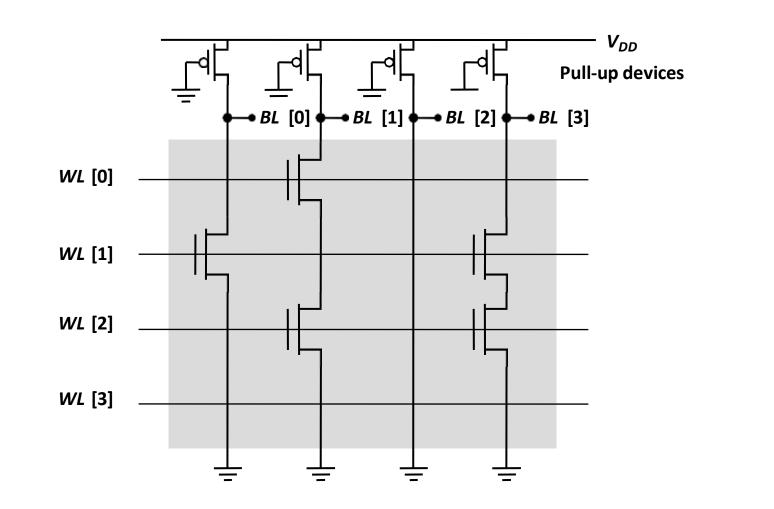

## **NOR-based ROM Array**

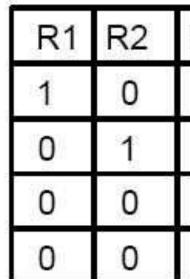

## **TRUTH TABLES**

## NAND-based ROM Array

| R1 | R2 | R3 | R4 | C1 | C2 | C3 | C4 |

|----|----|----|----|----|----|----|----|

| 0  | 1  | 1  | 1  | 0  | 1  | 0  | 1  |

| 1  | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| 1  | 1  | 0  | 1  | 1  | 0  | 0  | 1  |

| 1  | 1  | 1  | 0  | 0  | 1  | 1  | 0  |

## **NOR-based ROM Array**

| R3 | R4 | C1 | C2 | C3 | C4 |

|----|----|----|----|----|----|

| 0  | 0  | 0  | 1  | 0  | 1  |

| 0  | 0  | 0  | 0  | 1  | 1  |

| 1  | 0  | 1  | 0  | 0  | 1  |

| 0  | 1  | 0  | 1  | 1  | 0  |

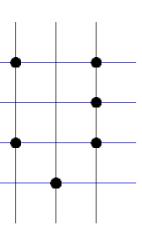

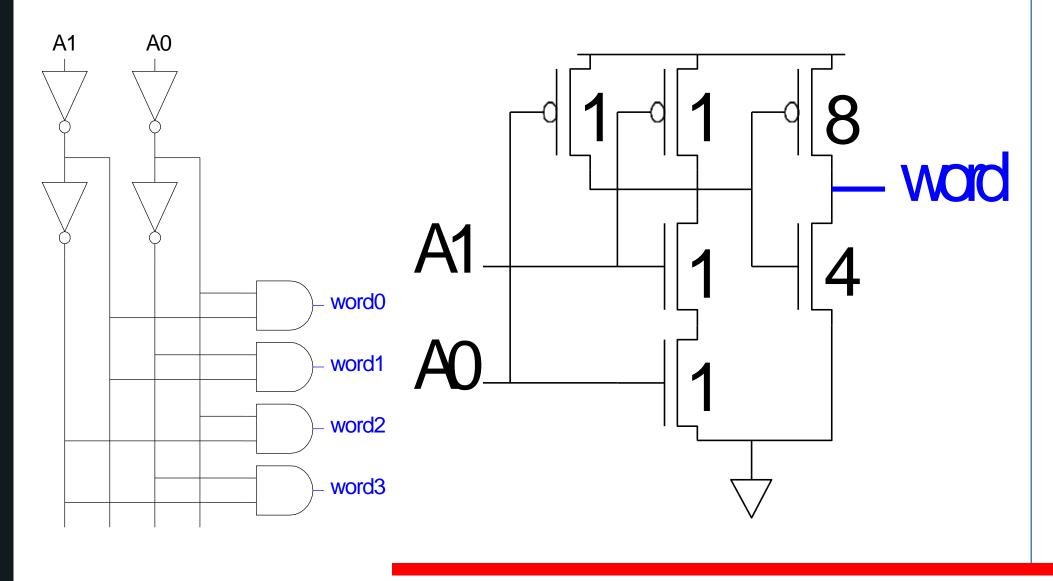

## **ROM EXAMPLE**

- 4-word x 6-bit ROM

- Represented with dot diagram

- Dots indicate 1's in ROM

Word 0: **010101** Word 1: **011001** Word 2: **100101** Word 3: **101010**

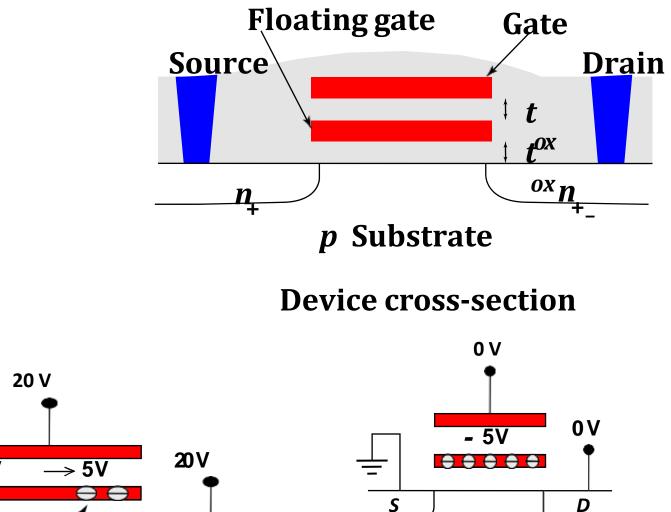

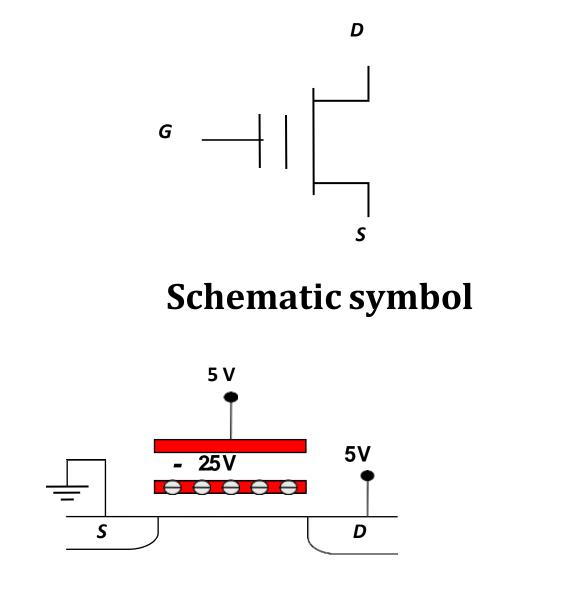

## NON-VOLATILE MEMORIES THE FLOATING-GATE TRANSISTOR (FAMOS)

Removing programming voltage leaves charge trapped

20 V  $0V \rightarrow 5V \qquad 20V$   $s \rightarrow 6 \leftrightarrow D$

Avalanche injection

#### Programming results in

### higher $V_{\tau}$

- •Decoders

- Sense Amplifiers

- Input/Output Buffers

- Control / Timing Circuitry

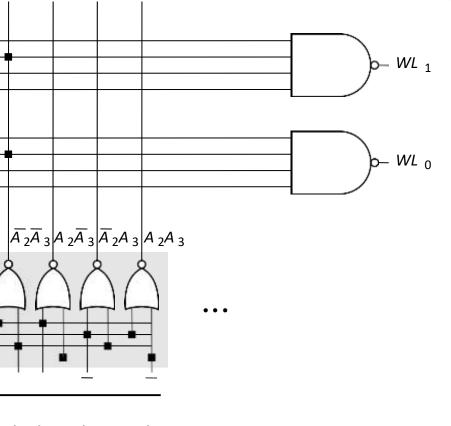

#### **Row Decoders**

- •Collection of 2<sup>M</sup> complex logic gates

- •Organized in regular and dense fashion

### (N)AND Decoder

### **NOR Decoder**

$$WL_{0} = \overline{A_{0} + A_{1} + A_{2} + A_{3} + A_{4} + A_{4}}$$

$$WL_{511} = \overline{A_{0} + \overline{A_{1}} + \overline{A_{2}} + \overline{A_{3}} + \overline{A_{4}} + \overline{A_{4$$

8A9

$^{A}8^{A}9$

$5^{+A}6^{+A}7^{+A}8^{+A}9$  $\overline{A}_5 + \overline{A}_6 + \overline{A}_7 + \overline{A}_8 + \overline{A}_9$

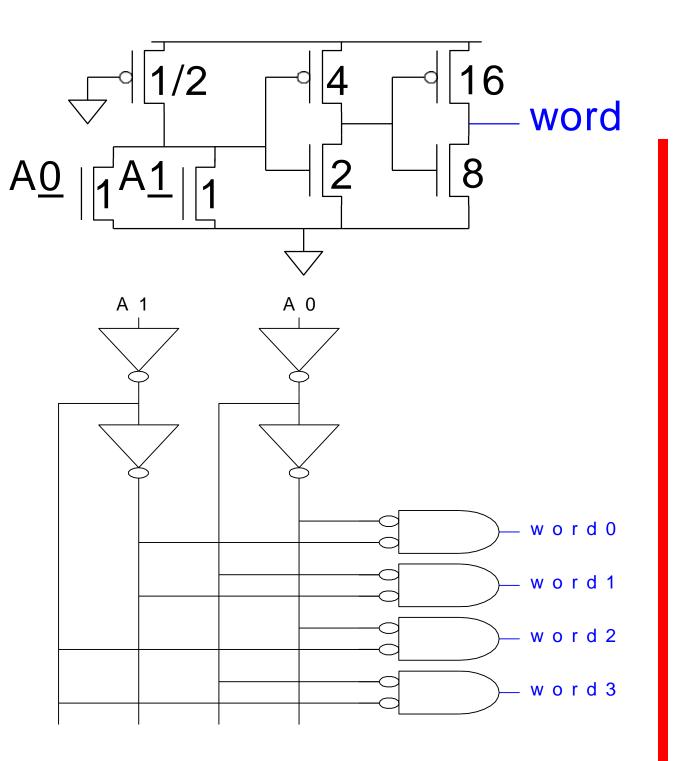

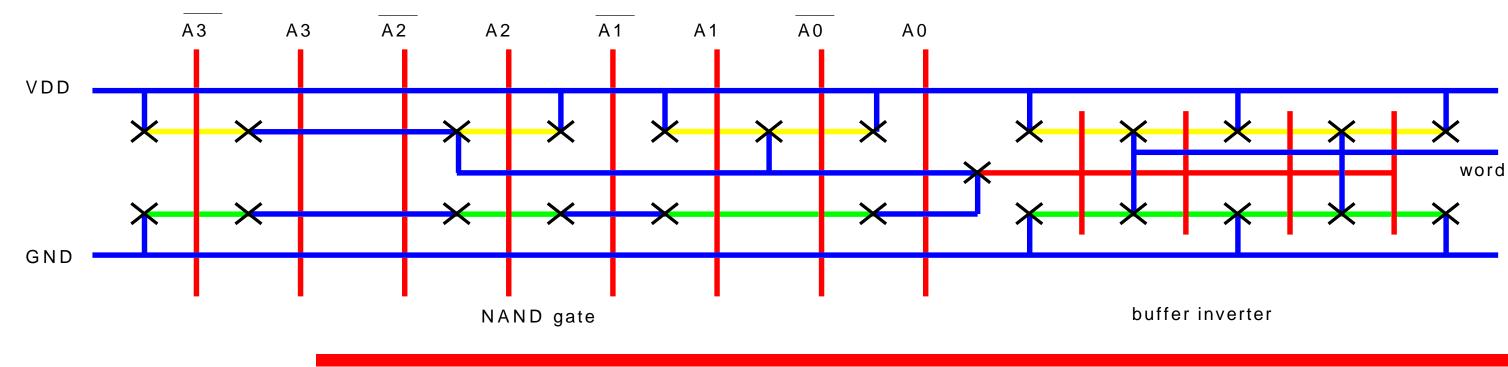

## **DECODERS**

- n:2<sup>n</sup> decoder consists of 2<sup>n</sup> n-input AND gates

- One needed for each row of memory

- Build AND from NAND or NOR gates

#### **Static CMOS**

#### Pseudo-nMOS

## **DECODER LAYOUT & HIERARCHICAL DECODERS**

$\overline{A_0A_1}A_0\overline{A_1}\overline{A_0A_1}A_0A_1$

$A_1$

$A_1A_0 \quad A_0$

NAND decoder using 2-input pre-decoders

•Decoders must be pitch-matched to SRAM cell Requires very skinny gates

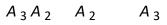

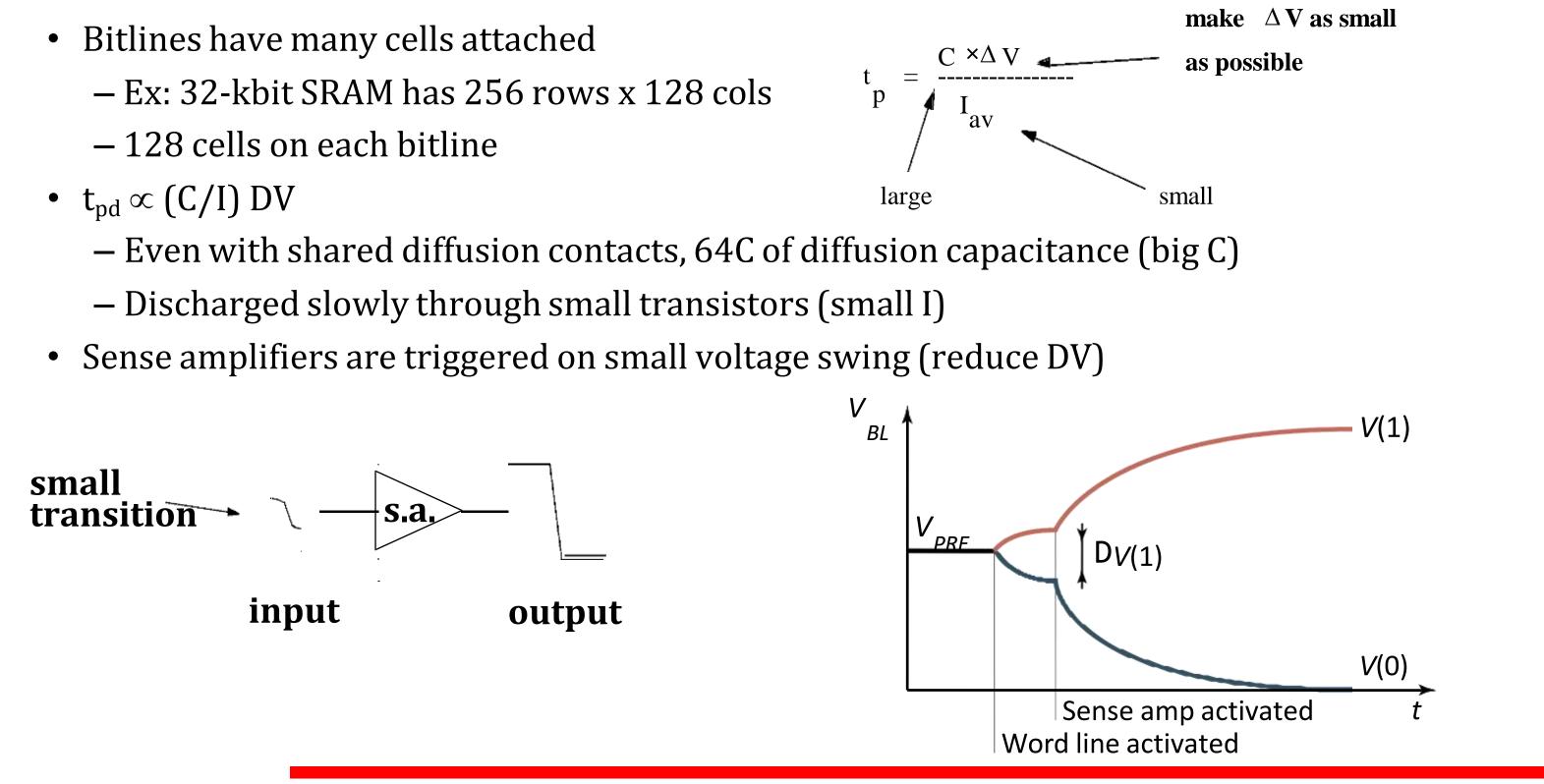

## **SENSE AMPLIFIERS**

- Bitlines have many cells attached

## **DIFFERENTIAL SENSE AMPLIFIER**

#### Directly applicable to SRAMs

19/9/2024

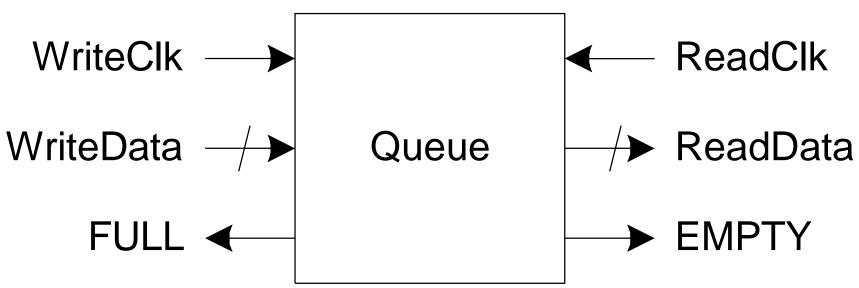

## **QUEUES**

- •Queues allow data to be read and written at different rates.

- •Read and write each use their own clock, data

- •Queue indicates whether it is full or empty

- •Build with SRAM and read/write counters (pointers)

## PLAs

- A Programmable Logic Array performs any function in sum-of-products form.

- Literals: inputs & complements

- Products / Minterms: AND of literals

- Outputs: OR of Minterms

- Example: Full Adder

$$s = a\overline{b}\overline{c} + \overline{a}b\overline{c} + \overline{a}\overline{b}c + abc$$

$$c_{\text{out}} = ab + bc + ac$$

## **ASSESSMENTS**

- 1. List out the memory classification

- 2. Compare ROM VS RAM

- 3. Differentiate DRAM VS SRAM

- 4. Draw the 6T SRAM CELL

- 5. Draw the Static CAM Memory Cell

- 6. Compare NAND-based & NOR based ROM Array

- 7. Write short notes on SENSE AMPLIFIERS

- 8. Draw the PLAs logic diagram.

19/9/2024

## **SUMMARY& THANK YOU**

19/9/2024