# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++'(III Cycle) Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

# **23ECB201 – DIGITAL SYSTEMS DESIGN**

#### II YEAR/ III SEMESTER

**UNIT 2 – COMBINATIONAL CIRCUITS**

**TOPIC- HALF ADDER**

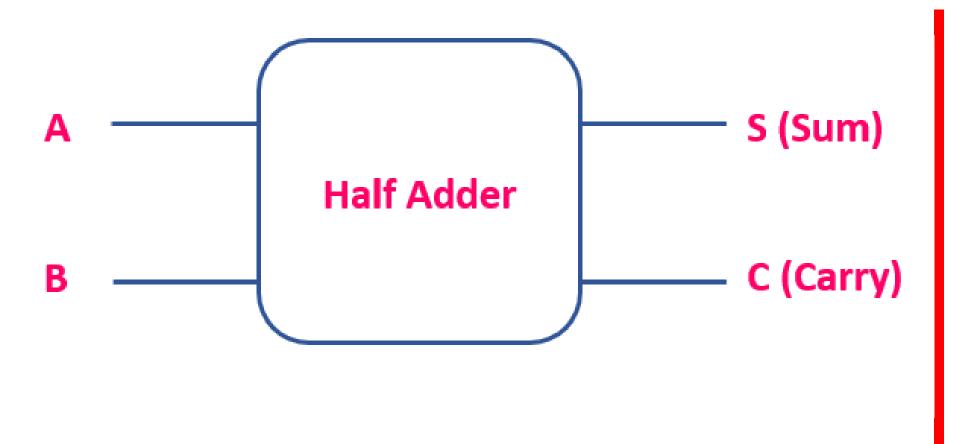

## HALF ADDER

- A half adder is a digital logic circuit that performs binary addition of two single-bit binary numbers.

- Half adder is a combinational arithmetic circuit that adds two numbers and produces a sum bit (s) and carry bit (c) both as output.

- The input variables are augend and addend bits and output variables are sum & carry bits.

#### **TRUTH TABLE**

| Bina |   |   |

|------|---|---|

| 0    | + | 0 |

| 0    | + | 1 |

| 1    | + | 0 |

| 1    | + | 1 |

| Α | B | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

Half Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT

#### ary Addition

- $\mathbf{0} = \mathbf{0}$

- = 1

- ) = 1

- 1 + 1 = 10

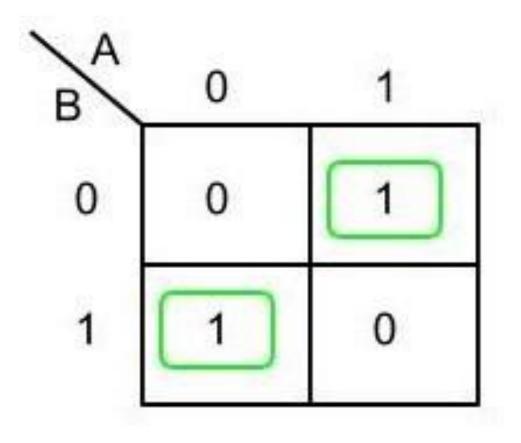

#### LOGICAL EXPRESSION

#### **FOR SUM**

15/09/2024

Half Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT

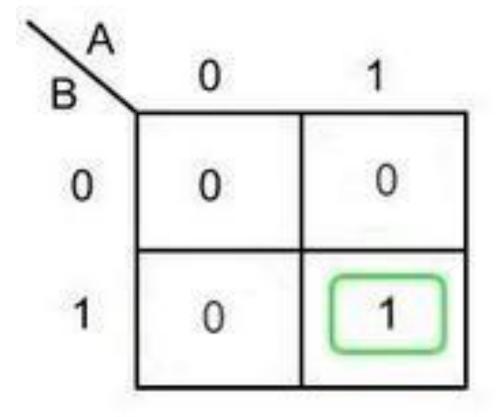

#### **FOR CARRY**

Carry,C=A·B

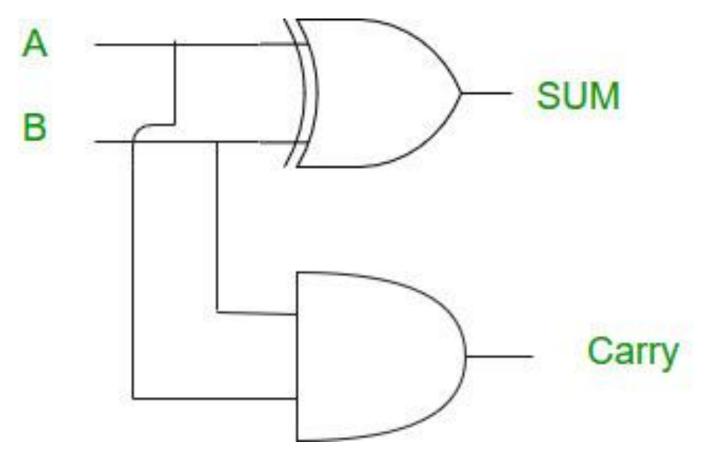

#### **IMPLEMENTATION**

#### Sum = A XOR B

Carry = A AND B

15/09/2024

Half Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT

### **APPLICATIONS OF HALF ADDER**

- 1.Arithmetic circuits

- 2.Data handling

- 3.Address unraveling

- 4. Encoder and decoder circuits

- 5. Multiplexers and demultiplexers

- 6.Counters

## **ADVANTAGES AND DISADVANTAGES**

#### **ADVANTAGES**

- Simplicity

- Speed

## **DISADVANTAGES**

- Limited Usefulness

- Lack of Convey Info

- **Propagation Deferral**

## **ASSESSMENT QUESTIONS**

Total number of inputs in a half adder is \_\_\_\_\_ 1.

a) 2

b) 3

c) 4

- d) 1

- 2. In which operation carry is obtained?

- a) Subtraction

#### b) Addition

c) Multiplication

d) Both addition and subtraction

3. If A and B are the inputs of a half adder, the sum is given by \_\_\_\_\_

- a) A AND B

- b) A OR B

- c) A XOR B

- d) A EX-NOR B

15/09/2024

Half Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT