# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++'(III Cycle) Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

## **DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING**

## **23ECB201 – DIGITAL SYSTEMS DESIGN**

#### II YEAR/ III SEMESTER

**UNIT 2 – COMBINATIONAL CIRCUITS**

**TOPIC- FULL ADDER**

#### **FULL ADDER**

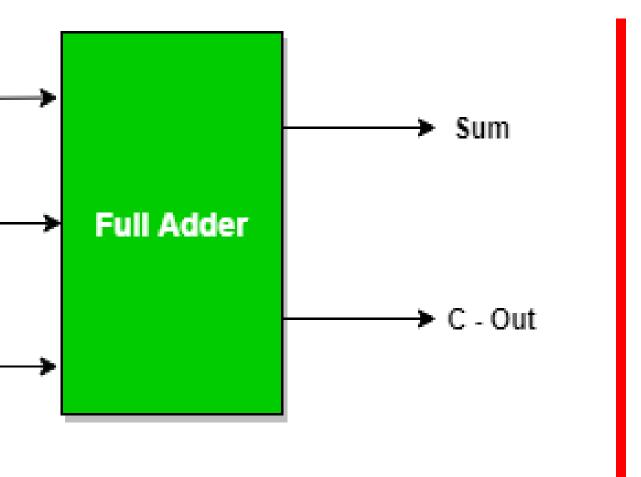

• Full Adder is the adder that adds three inputs and produces two outputs. • The first two inputs are A and B and the third input is an input carry as C-IN. C - IN · • The input variables are augend and addend bits and output variables are sum & carry bits.

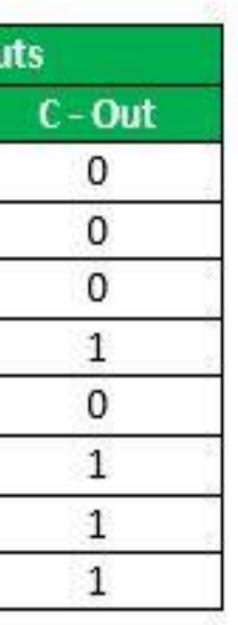

#### **TRUTH TABLE**

|   | Inputs |      |     | Outpu |  |

|---|--------|------|-----|-------|--|

| Α | B      | C-IN | Sum |       |  |

| 0 | 0      | 0    | 0   |       |  |

| 0 | 0      | 1    | 1   |       |  |

| 0 | 1      | 0    | 1   |       |  |

| 0 | 1      | 1    | 0   |       |  |

| 1 | 0      | 0    | 1   |       |  |

| 1 | 0      | 1    | 0   |       |  |

| 1 | 1      | 0    | 0   |       |  |

| 1 | 1      | 1    | 1   |       |  |

Full Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT

| <b>Binary Addition</b> |

|------------------------|

| 0 + 0 = 0              |

| 0 + 1 = 1              |

| 1 + 0 = 1              |

| 1 + 1 = 10             |

10 + 1 = 11

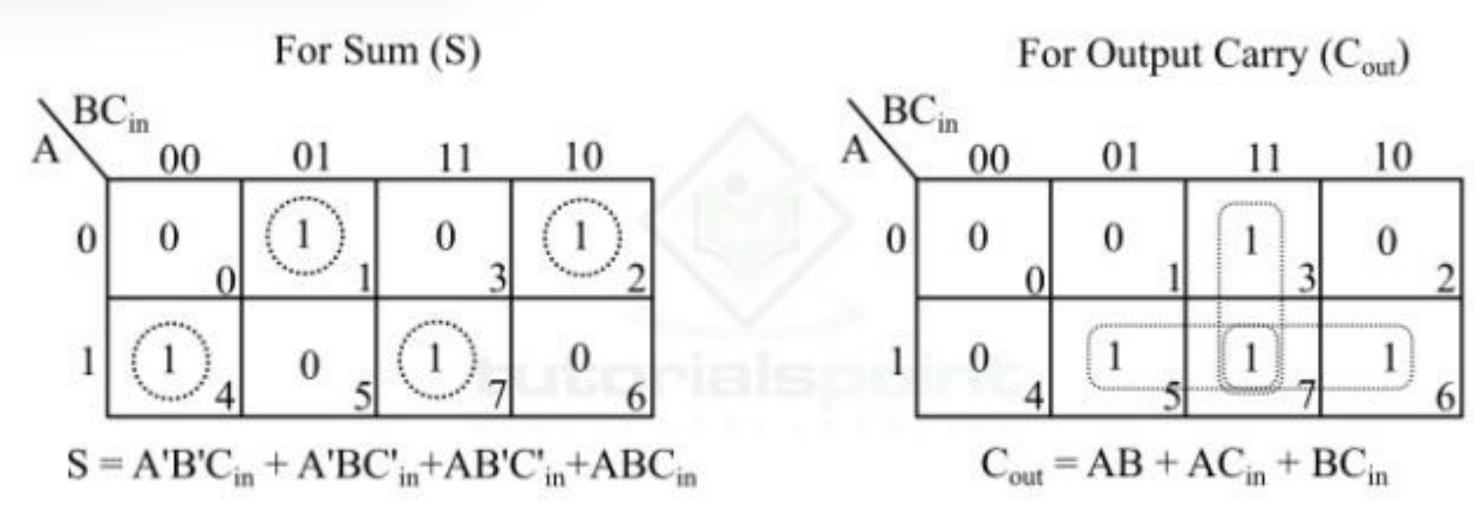

#### LOGICAL EXPRESSION

Full Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT

15/09/2024

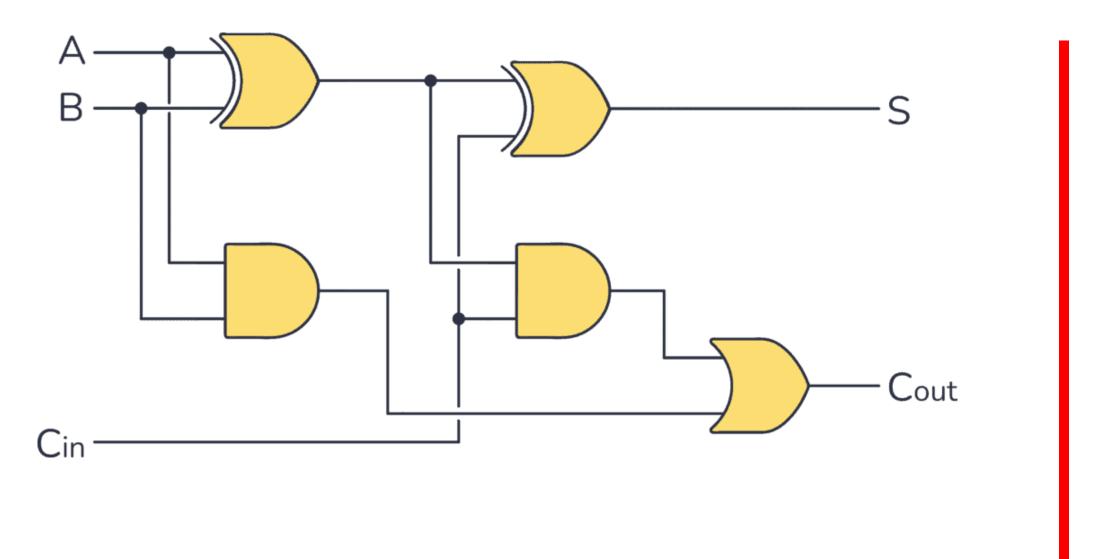

#### **IMPLEMENTATION**

#### $Sum,S=A \oplus B \oplus Cin$

15/09/2024

Full Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT

#### **APPLICATIONS OF FULL ADDER**

**1.**Arithmetic circuits 2.Data handling

3.Counters

4. Multiplexers and demultiplexers

5. Memory tending to

6. ALUs

#### **ADVANTAGES AND DISADVANTAGES**

#### **ADVANTAGES**

- Flexibility

- Carry Info

- Speed

### **DISADVANTAGES**

- Complexity

- **Propagation Deferral**

15/09/2024

Full Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT

### **ASSESSMENT QUESTIONS**

Total number of inputs in a Full adder is \_\_\_\_\_

a) 2 **b)** 3

c) 4

d) 1

2. How many AND, OR and EXOR gates are required for the configuration a) 1, 2, 2 b) 2, 1, 2 c) 3, 1, 2 d) 4, 0, 1

3. The difference between half adder and full adder is a) Half adder has two inputs while full adder has four inputs b) Half adder has one output while full adder has two outputs c) Half adder has two inputs while full adder has three inputs d) All of the Mentioned

15/09/2024

Full Adder/23EBC201/ Digital Systems Design / K.SURIYA/ECE/SNSCT