10/17/202

# **SNS COLLEGE OF TECHNOLOGY**

**Coimbatore-35 An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## **19ECB302–VLSI DESIGN**

#### III YEAR/ V SEMESTER

## UNIT III-SEQUENTIAL LOGIC CIRCUITS

**TOPIC 1-STATIC LATCHES AND DYNAMIC REGISTERS**

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

#### OUTLINE

- LATCH VERSUS REGISTER

- LATCH-BASED DESIGN

- MUX,

- MASTER SLAVE REGISTER

- ACTIVITY

- TIME, CLK BASED LATCHES

- PULSE-TRIGGERED LATCHES

- SUMMARY

10/17/202<mark>4</mark>

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

# **Introduction – Latches and Registers**

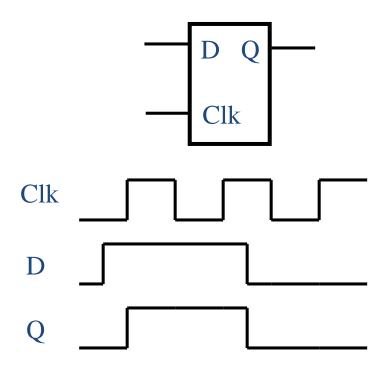

#### REGISTER

$\succ$  Used to hold the system state. Clock pulse is applied to the registers. On the rising edge of the clock pulse, the next state bits are copied to the output of the registers .

#### **Two Types**

- **1. Positive edge triggered –** input is copied on positive edge of clock.

- 2. Negative edge triggered input is copied on negative edge of clock. LATCH

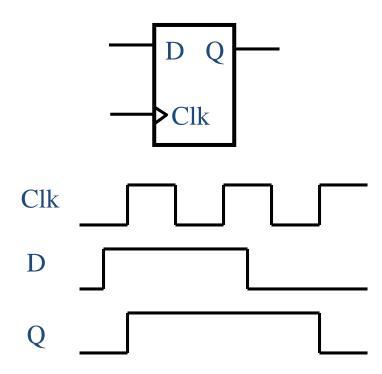

- > Level sensitive circuit which is used to pass the D input to the Q output when clock is high.

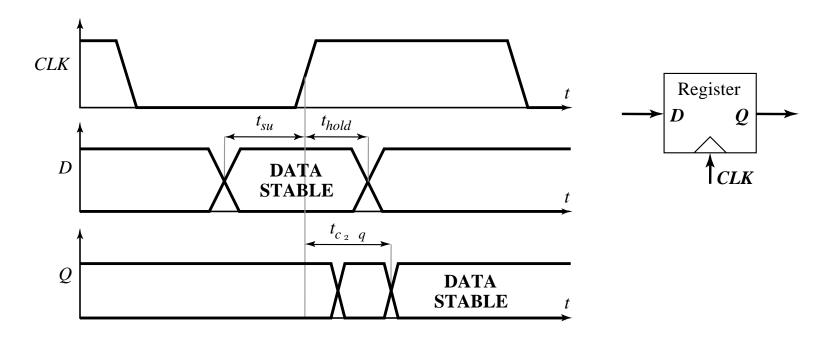

#### **SET UP TIME**

$\succ$  Time during which the data input is valid before the transition of the clock pulse. **HOLD TIME**

$\succ$  Time during which the data input remains valid after the edge of the clock pulse. **CONTAMINATION DELAY** – Minimum Delay

#### LATCH VERSUS REGISTER

• Latch stores data when clock is low

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

• Register stores data when clock rises

#### LATCHES

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

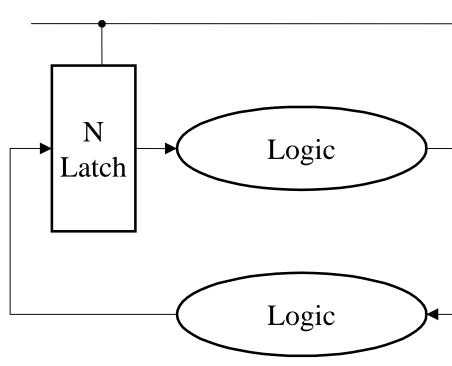

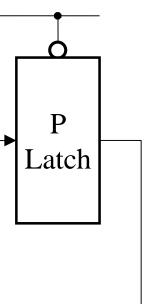

### **LATCH-BASED DESIGN**

• N latch is transparent when f = 0

when f = 1

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

# • P latch is transparent

#### **TIMING DEFINITIONS**

10/17/2024

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

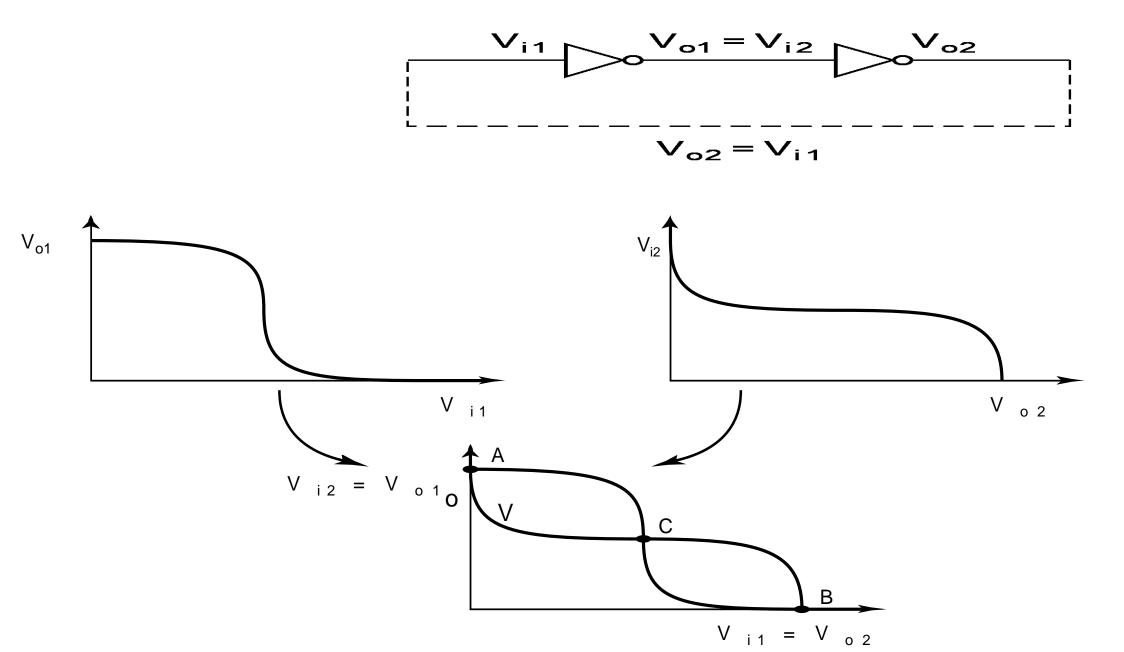

#### **POSITIVE FEEDBACK: BI-STABILITY**

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

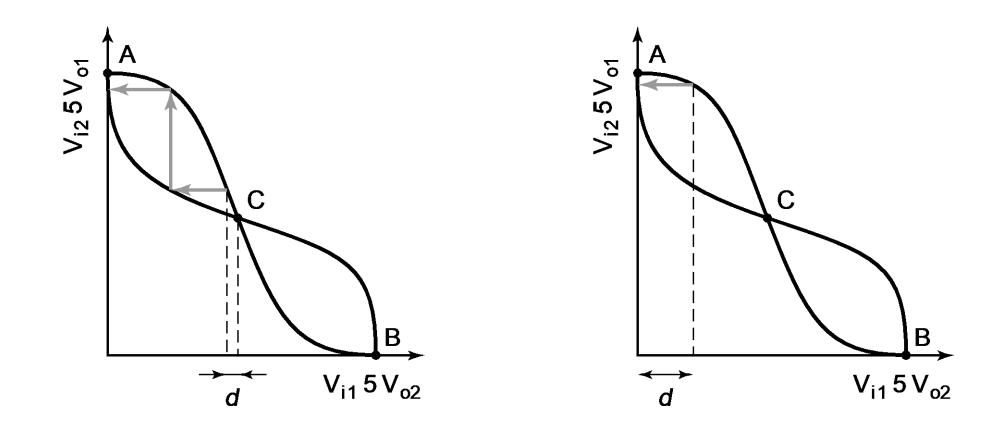

#### **META-STABILITY**

#### Gain should be larger than 1 in the transition region

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

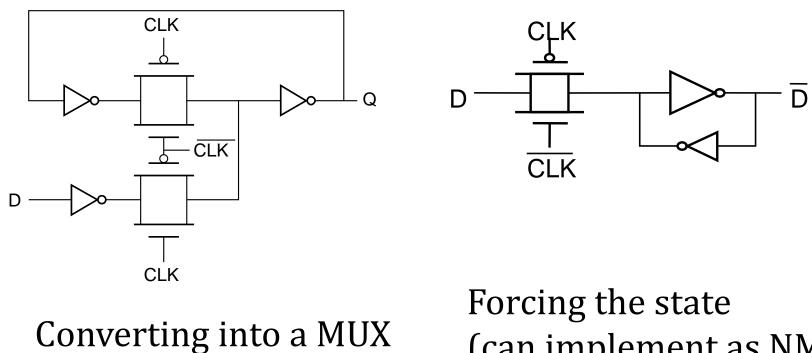

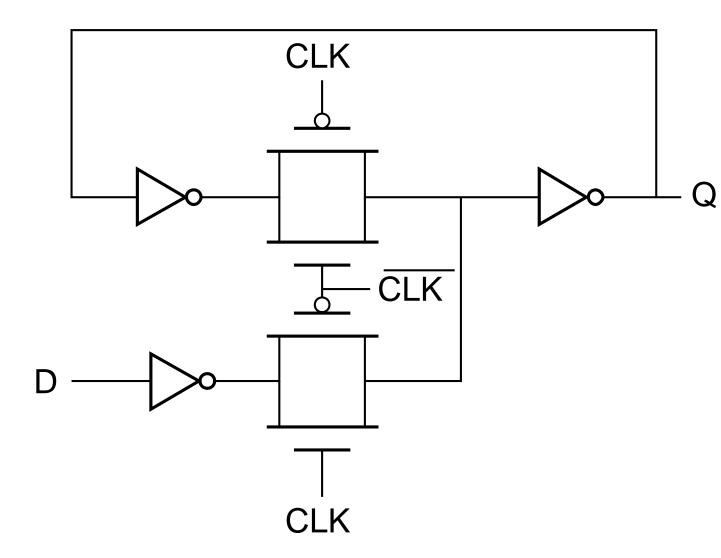

# WRITING INTO A STATIC LATCH

Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

# (can implement as NMOS-only)

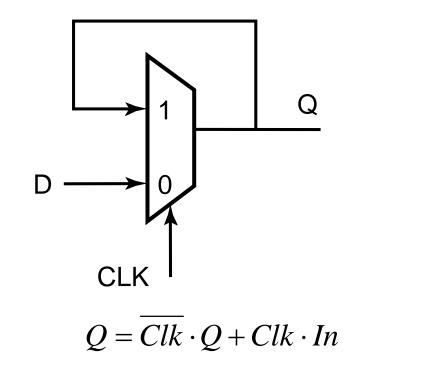

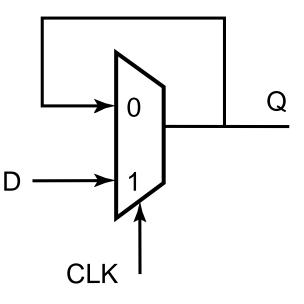

#### **MUX-BASED LATCH**

10/17/2024

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

#### **MUX-BASED LATCHES**

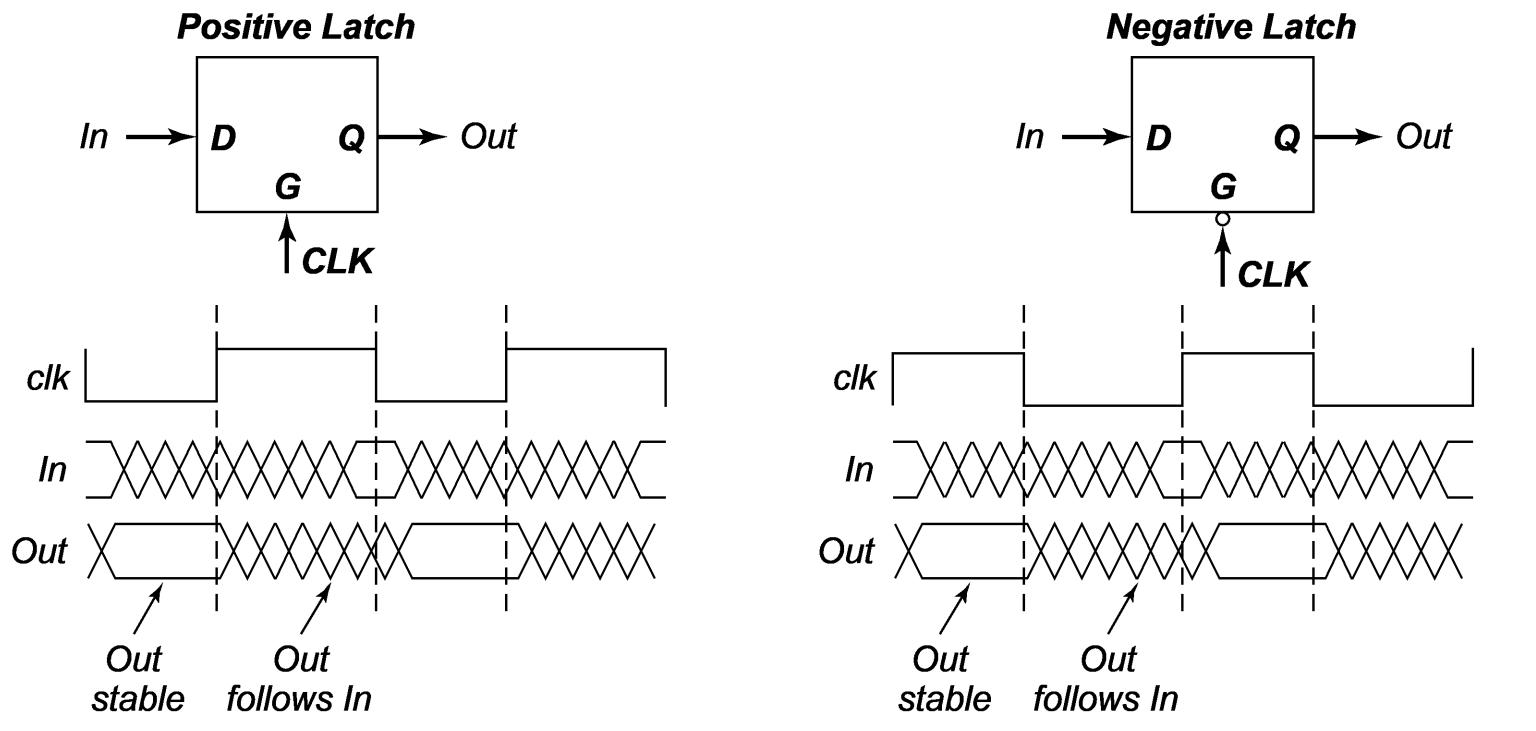

**Negative latch** (transparent when CLK= 0)

10/17/2024

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

#### **Positive latch** (transparent when CLK= 1)

$Q = Clk \cdot Q + \overline{Clk} \cdot In$

#### **MUX-BASED LATCH**

NMOS only

10/17/2024

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

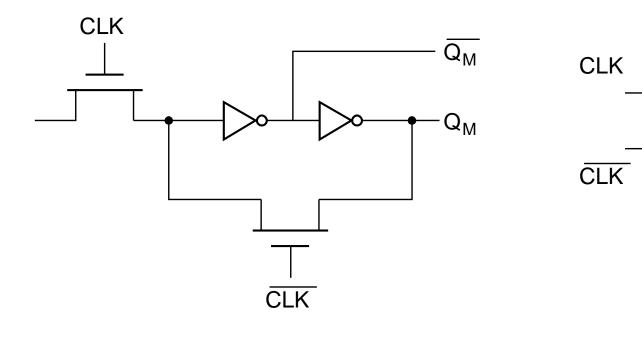

#### Non-overlapping clocks

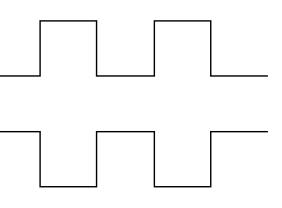

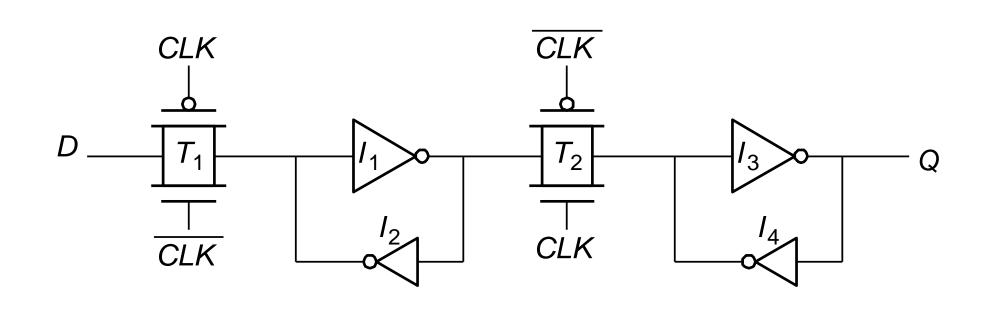

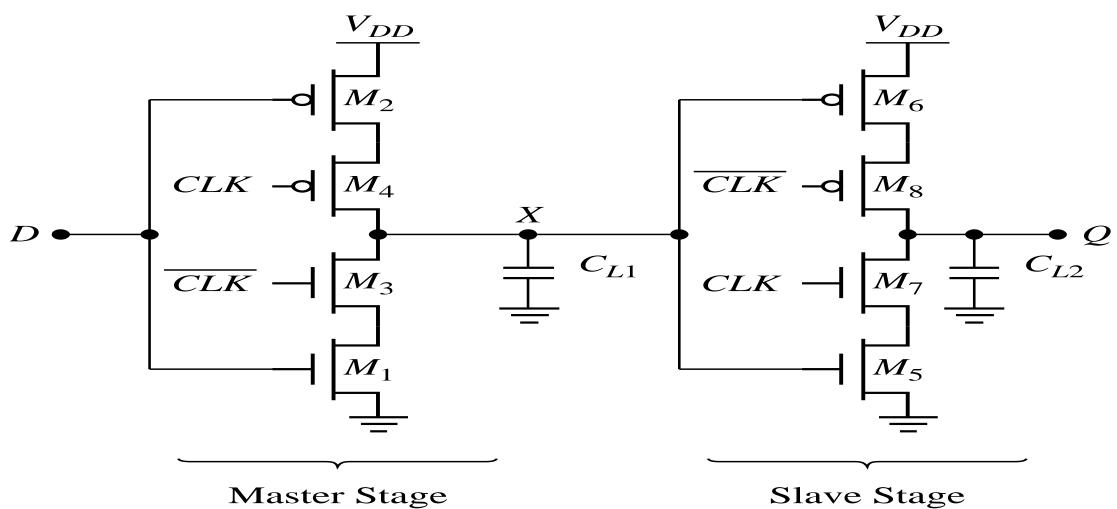

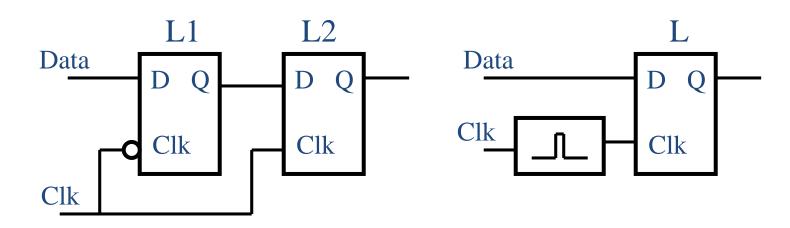

#### **MASTER-SLAVE (EDGE-TRIGGERED) REGISTER**

Two opposite latches trigger on edge Also called master-slave latch pair

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

#### **MASTER-SLAVE REGISTER**

#### Multiplexer-based latch pair

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

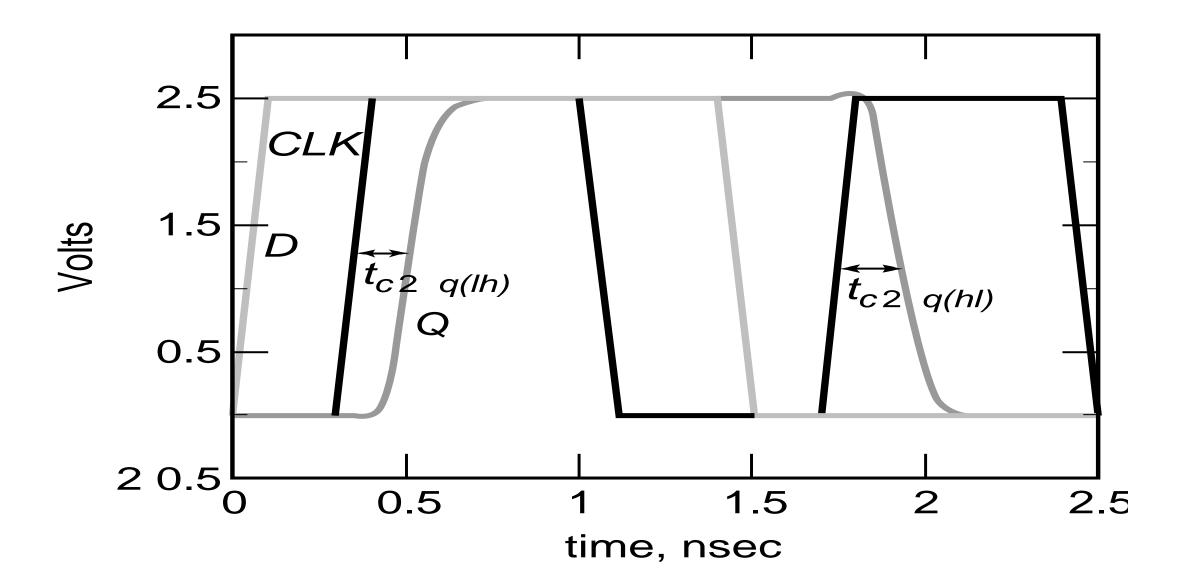

**CLK-Q DELAY**

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

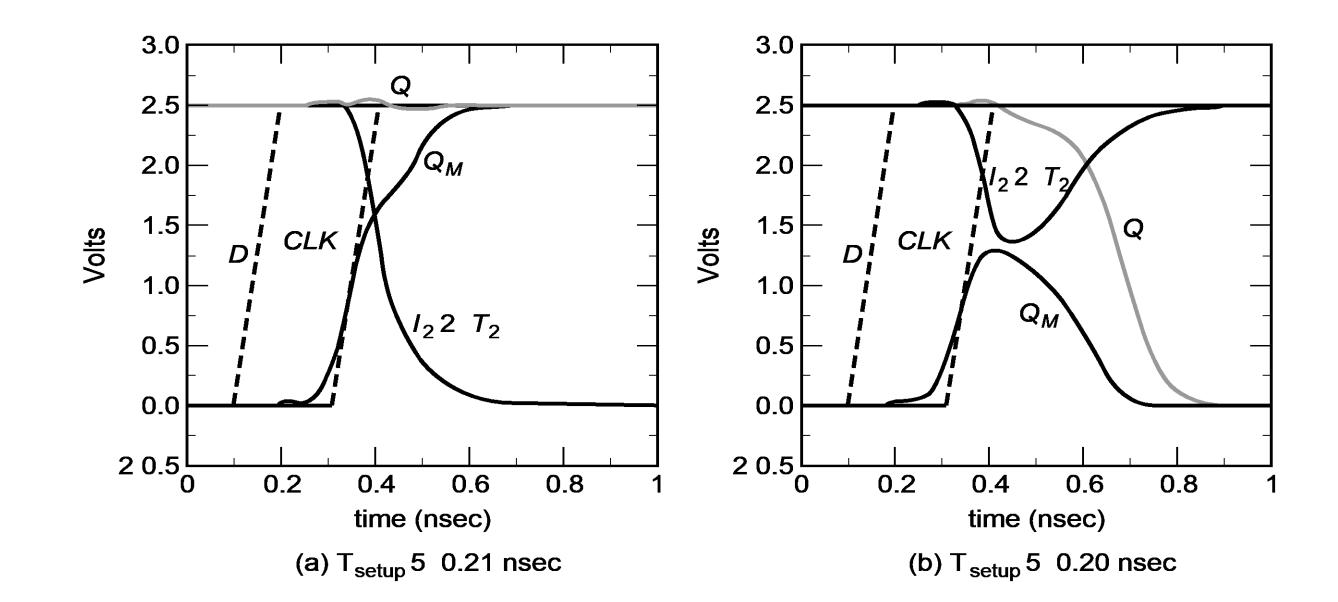

**SETUP TIME**

10/17/2024

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

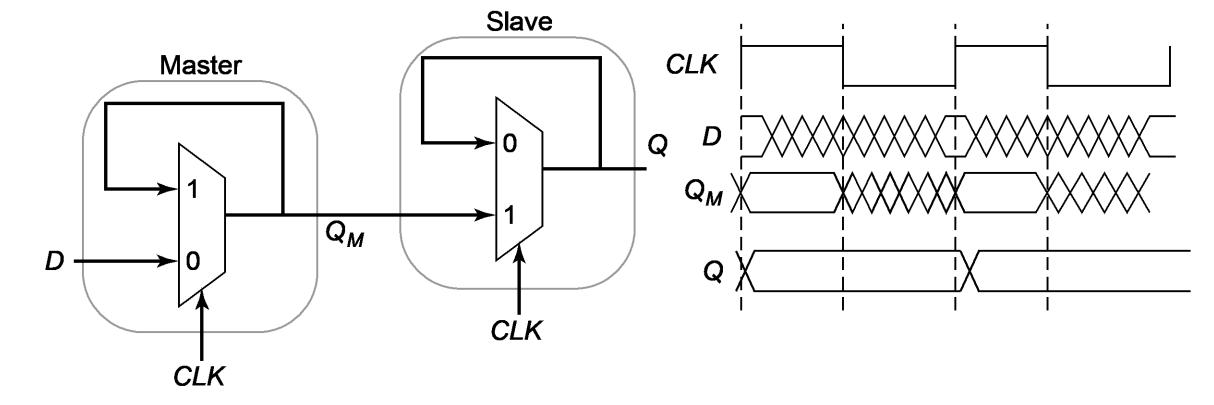

#### **REDUCED CLOCK LOAD MASTER-SLAVE REGISTER**

10/17/2024

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

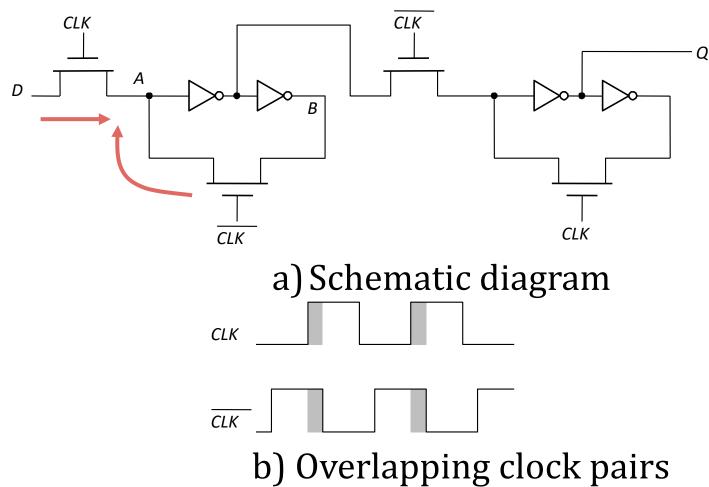

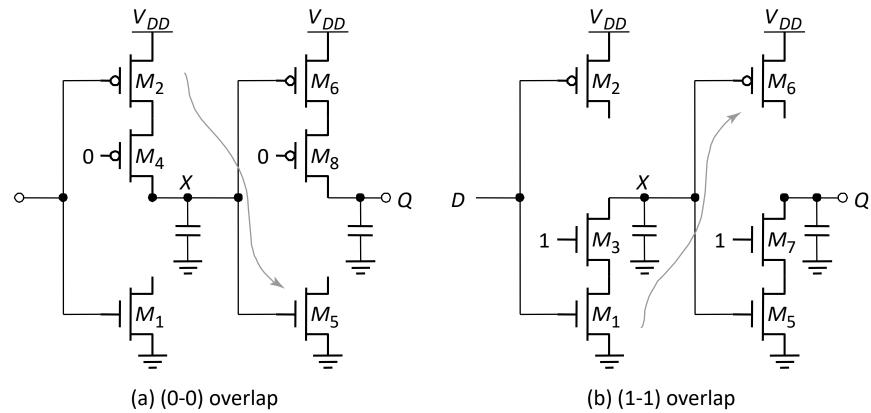

#### **AVOIDING CLOCK OVERLAP**

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

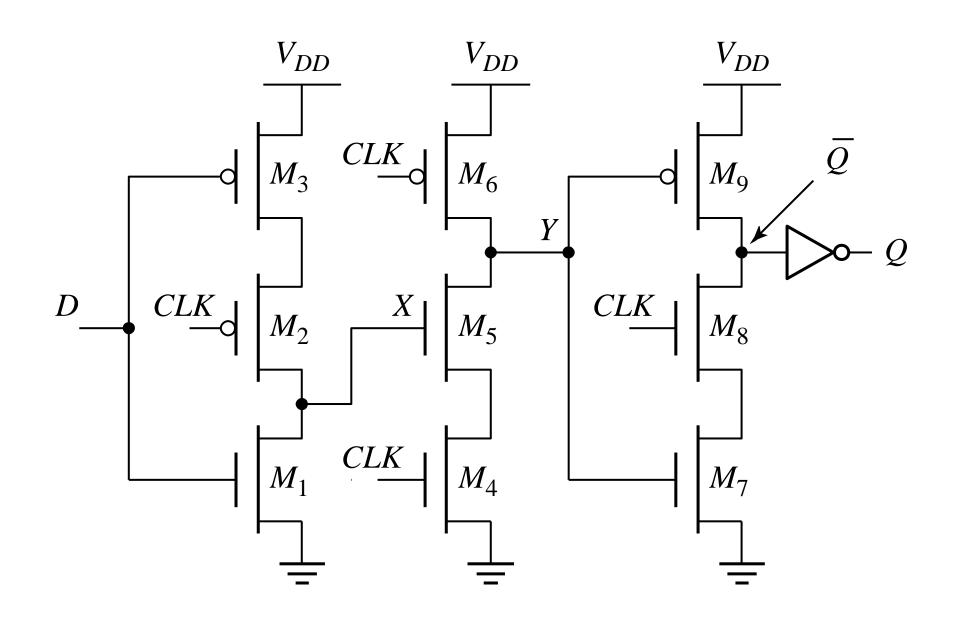

#### **OTHER LATCHES/REGISTERS:** C<sup>2</sup>MOS

"Keepers" can be added to make circuit pseudo-static

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

### **INSENSITIVE TO CLOCK-OVERLAP**

$\mathbf{A}$

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

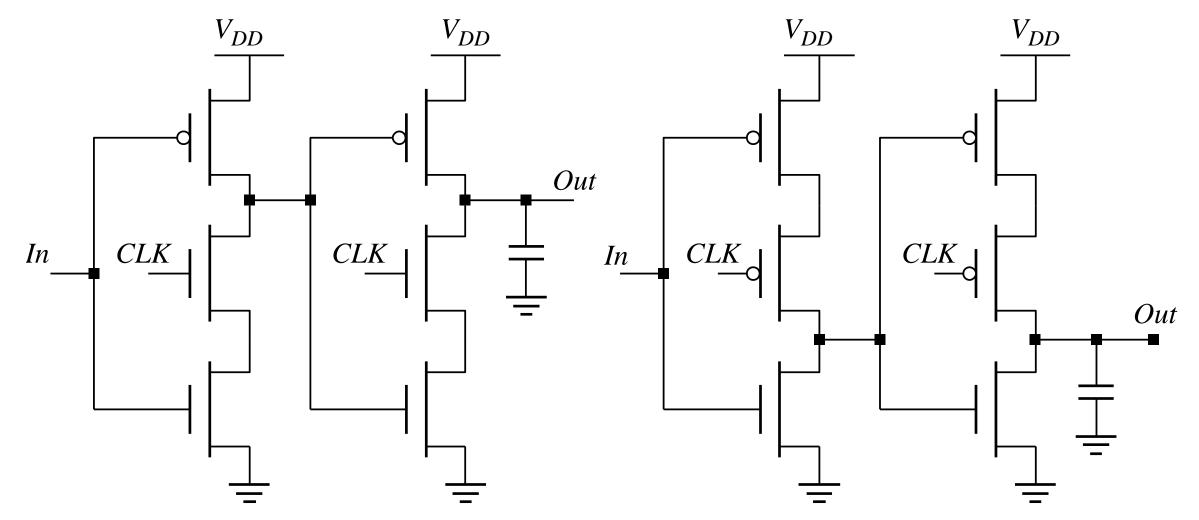

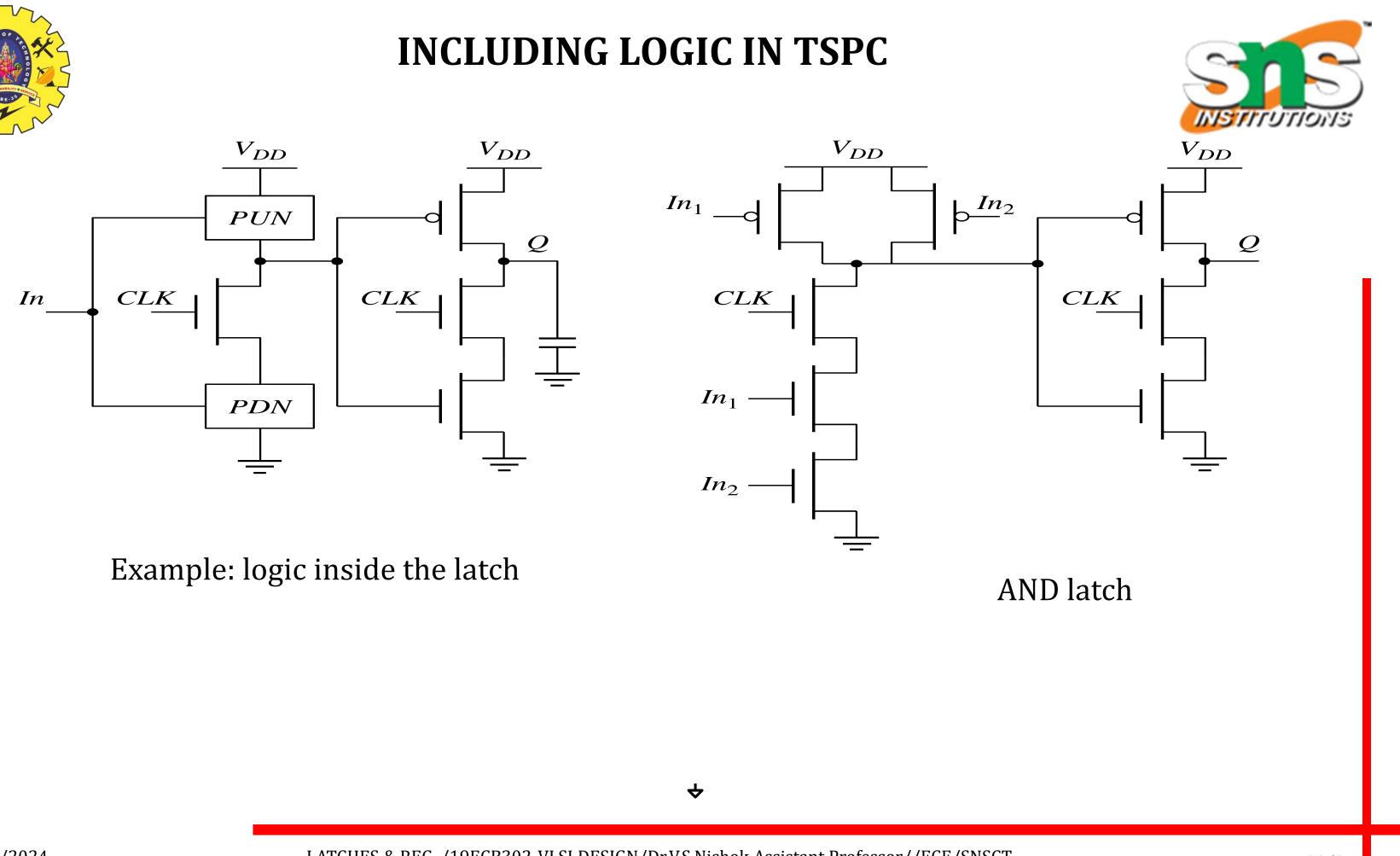

# **OTHER LATCHES/REGISTERS: TSPC**

#### Positive latch (transparent when CLK= 1)

Negative latch (transparent when CLK= 0)

$\mathbf{A}$

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

10/17/2024

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

#### **TSPC REGISTER**

$\mathbf{A}$

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

## **PULSE-TRIGGERED LATCHES AN ALTERNATIVE APPROACH**

Ways to design an edge-triggered sequential cell:

Master-Slave Latches

Pulse-Triggered Latch

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT

10/17/2024

#### ASSESSMENT

- 1. Compare Latch vs Register

- 2. Define Bi stability

- 3. Draw Master slave flip flop using latches

#### **SUMMARY & THANK YOU**

10/17/2024

LATCHES & REG. /19ECB302-VLSI DESIGN/Dr.V.S.Nishok Assistant Professor//ECE/SNSCT