(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

Topic 2.7: FET Amplifiers-Small signal analysis of CS amplifier with fixed bias.

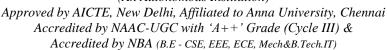

#### JEET Amplifiers \* It provide an encellent Voltage gain (Av) with The added advantage of a high Input Impedance (Ii). \* For this reason JEETA are often preferred over BJTs for certain types of applications. \* There are 3 basic configurations 1. Common Source 2. Lommon Drain (source follower) 3. common Grate \* The difference between BJT 4 JE ET configurations: JFET It controls large output It controls large output current (II) by means of a current (ID) by means of a small input voltage relative small input cument ( Vg) (Tb). Small Signal Analysis of JFET Amplifiers

- \* The Drain to Source Current of JFET is controlled by gate to source Voltage.

- \* The change is the drain current due to change is gate to source voltage can be determined using the transconditation of the drain change is gate.

\* Another important parameter is drain resistance 8d.

$$r_d = \frac{\Delta V_{DS}}{\Delta I_D} / v_{as} = constant$$

.

(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

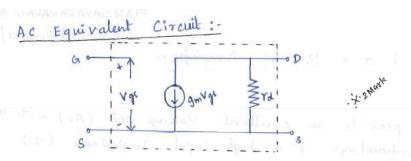

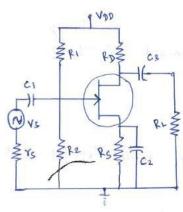

Fig: M-channel JFET- CS

\* the relation of Id is included as current source ymvqs connected from drain to source.

\* The imput impedance is represented by The open circuit at it's input terminal, since I'm is zero.

\* The Output impedance is represented by rd from drain to source

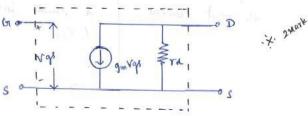

Appronimate Ac Equivalent circuit:

\* When The value of enternal drain resistance Rp is very small as compared to the value of output impedance represented by rd, it's possible to replace rd by open circuit.

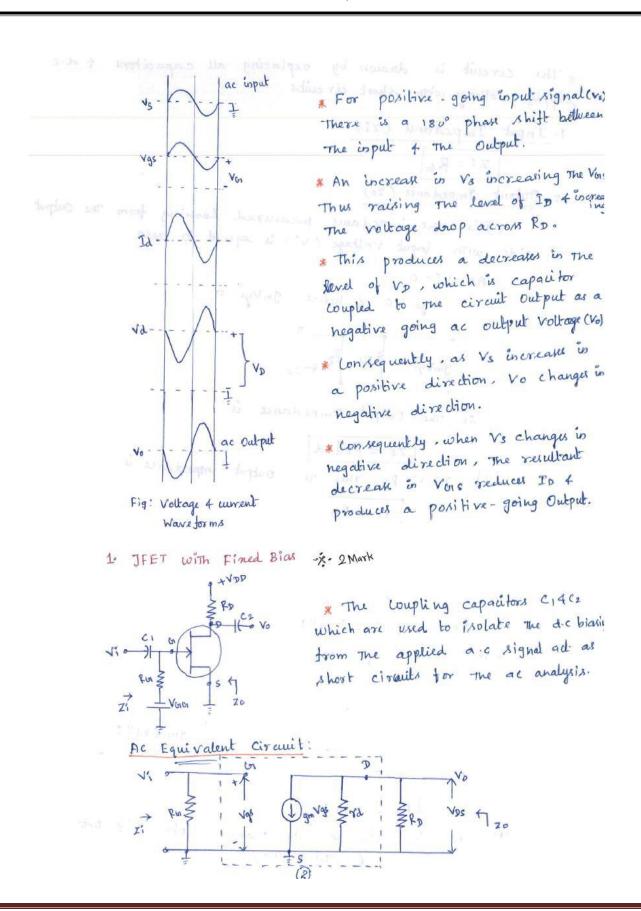

1. Common Source Circuit Analysis

Source, 4 The Output terminals are The Drain 4 The Source.

\* So The source terminal is common to both input 4 output. 4 The circuit. configuration is known as common soura (a

(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

(An Autonomous Institution)

COIMBATORE-641 035, TAMIL NADU

\* The circuit is drawn by replacing all capacitors of d.c supply voltage with short circuits. 1. Input Impedance (zi) 2. Output Impedance (20) It's The impedance measured looking from the output side with input voltage (vi) is equal to zero. AB Vi= 0 vgs = 0 4 hence gmvgs = 0 The Output Impedance is output impedance 16 rd >> Rp Then The 3. Voltage Gain (AV)  $Av = \frac{Vds}{Vqs} = \frac{Vo}{Vi}$ Vo = - gm Vgs (rd || RD) \* W. K. T Vi = Vgs Then Vo = - gm Vi (rdll Rp)  $Av = \frac{-g_m v/r}{v/r} \left( rd \parallel R b \right)$ \* it rd>>RD

Av ~ -9mRD

\*The negative sign indicate Thore is a phone shift Det 180° between The is put & output Volkages.