## **SNS COLLEGE OF TECHNOLOGY**

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A++' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ARTIFICIAL INTELLIGENCE AND MACHINE LEARNING

19ECB231 – DIGITAL ELECTRONICS

1

II YEAR/ III SEMESTER

UNIT 1 – MINIMIZATION TECHNIQUES AND LOGIC GATES

TOPIC -LOGIC GATES

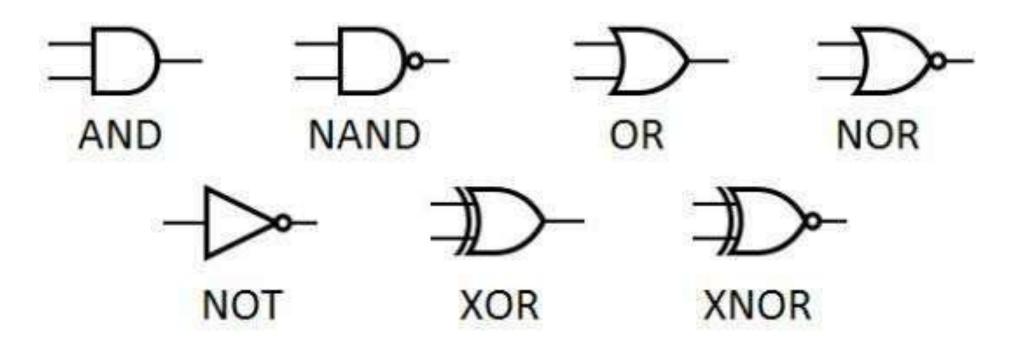

# **LOGIC GATES**

- AND

- OR

- NOT

- NAND

- NOR

- XOR

- XNOR

## WHAT IS LOGIC GATE?

A Logic Gate is an idealized or physical electronic device which is used for implementing a boolean function, a logical operation performed on one or more binary inputs that produce a single binary output.

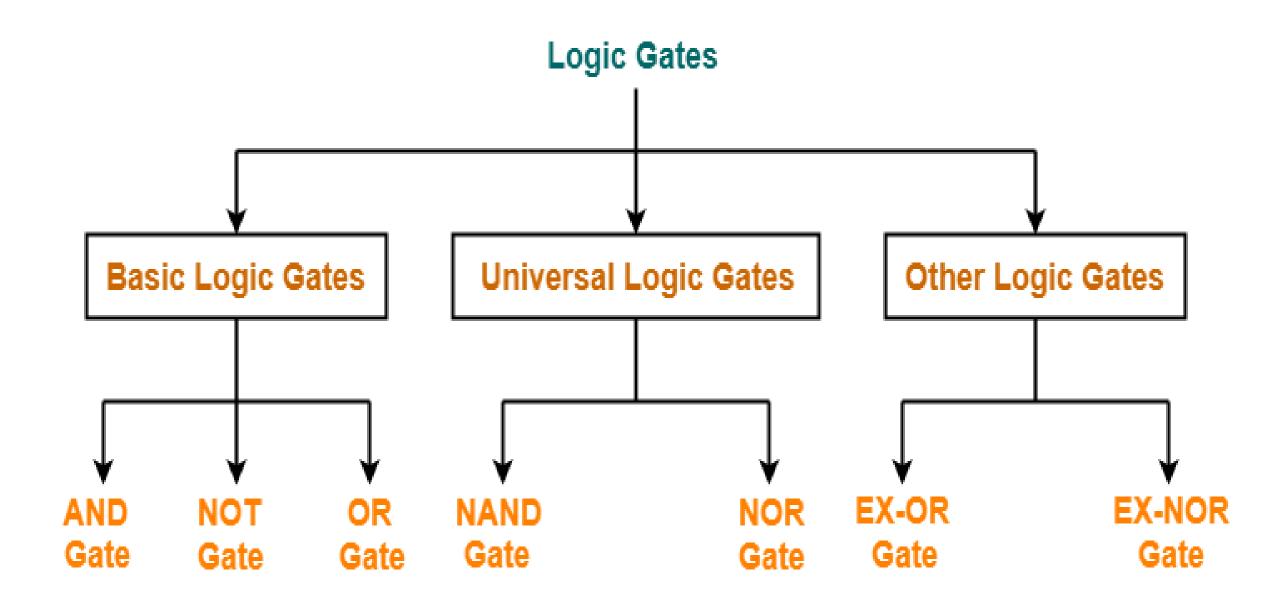

## **CLASSIFICATION OF LOGIC GATES**

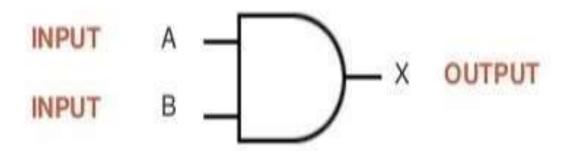

## **AND GATE**

The output will be positive (true) when both inputs (the input one AND the input two) are positive (true).

| INPUT |   | ОПТРИТ |

|-------|---|--------|

| А     | В | OUIFUI |

| 0     | 0 | 0      |

| 1     | 0 | 0      |

| 0     | 1 | 0      |

| 1     | 1 | 1      |

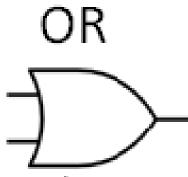

## **OR GATE**

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | OUTFUI |

| 0     | 0 | 0      |

| 1     | 0 | 1      |

| 0     | 1 | 1      |

| 1     | 1 | 1      |

In Boolean Algebra the OR function is the equivalent of addition so its output state represents the addition of its inputs.

In Boolean Algebra the OR function is represented by a "plus" sign (+) so for a two input OR gate the Boolean equation is given as:

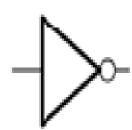

## **NOT GATE**

NOT

| INPUT | OUTPUT |

|-------|--------|

| Α     |        |

| 0     | 1      |

| 1     | 0      |

The NOT function is not a decision making logic gate like that of AND or OR gates, but instead it is used to invert or complement a digital signal. In other words, its output state will always be the opposite of its input state.

## **NAND GATE**

# NAND

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | OUIFUI |

| 0     | 0 | 1      |

| 1     | 0 | 1      |

| 0     | 1 | 1      |

| 1     | 1 | 0      |

- The term NAND is a contraction of NOT-AND and implies an AND function with a complemented(inverted) output.

- The output will be HIGH, when any one of the inputs is LOW and the output will be LOW when both the inputs are HIGH.

- This operation is opposite to that of AND Gate.

## **NOR GATE**

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | OUIFUI |

| 0     | 0 | 1      |

| 1     | 0 | О      |

| 0     | 1 | 0      |

| 1     | 1 | 0      |

- The term NOR is a contraction of NOT-OR and implies an OR function with a complemented(inverted) output.

- The output will be LOW, when any one of the inputs is HIGH and the output will be HIGH when both the inputs are LOW.

- This operation is opposite to that of OR Gate.

## **UNIVERSAL GATES**

- The NAND and NOR gates are used to generate AND,OR and NOT functions.

- Any logic logic function can be implemented using NAND and NOR gates. So it is called as Universal gates.

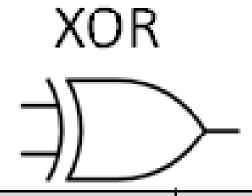

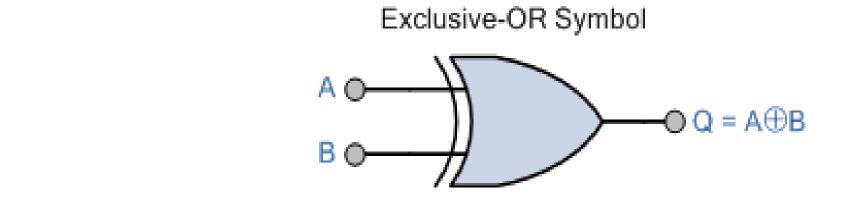

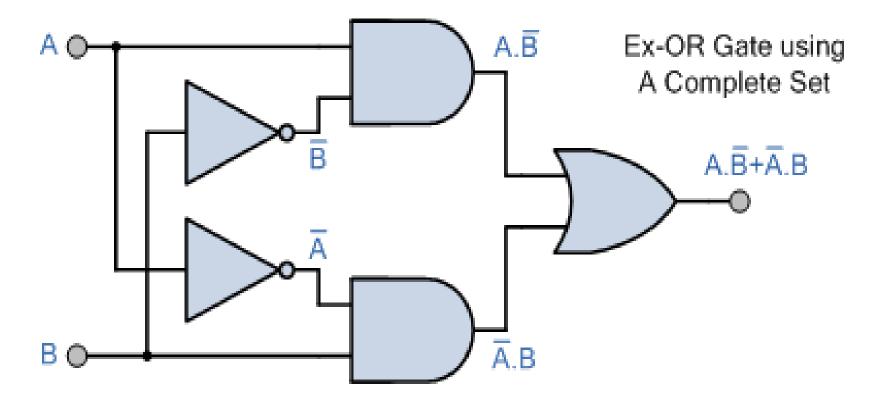

# **EX-OR GATE**

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | OUIFUI |

| 0     | 0 | 0      |

| 1     | 0 | 1      |

| 0     | 1 | 1      |

| 1     | 1 | 0      |

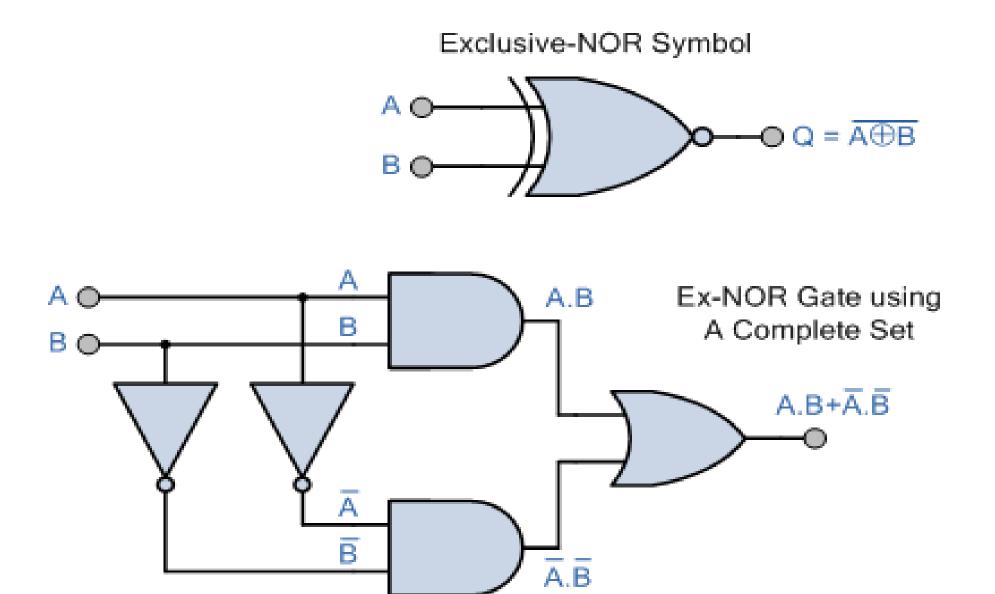

## **EX-NOR GATE**

| INPUT |   | OUTPUT |

|-------|---|--------|

| Α     | В | OUIFUI |

| 0     | 0 | 1      |

| 1     | 0 | О      |

| 0     | 1 | О      |

| 1     | 1 | 1      |

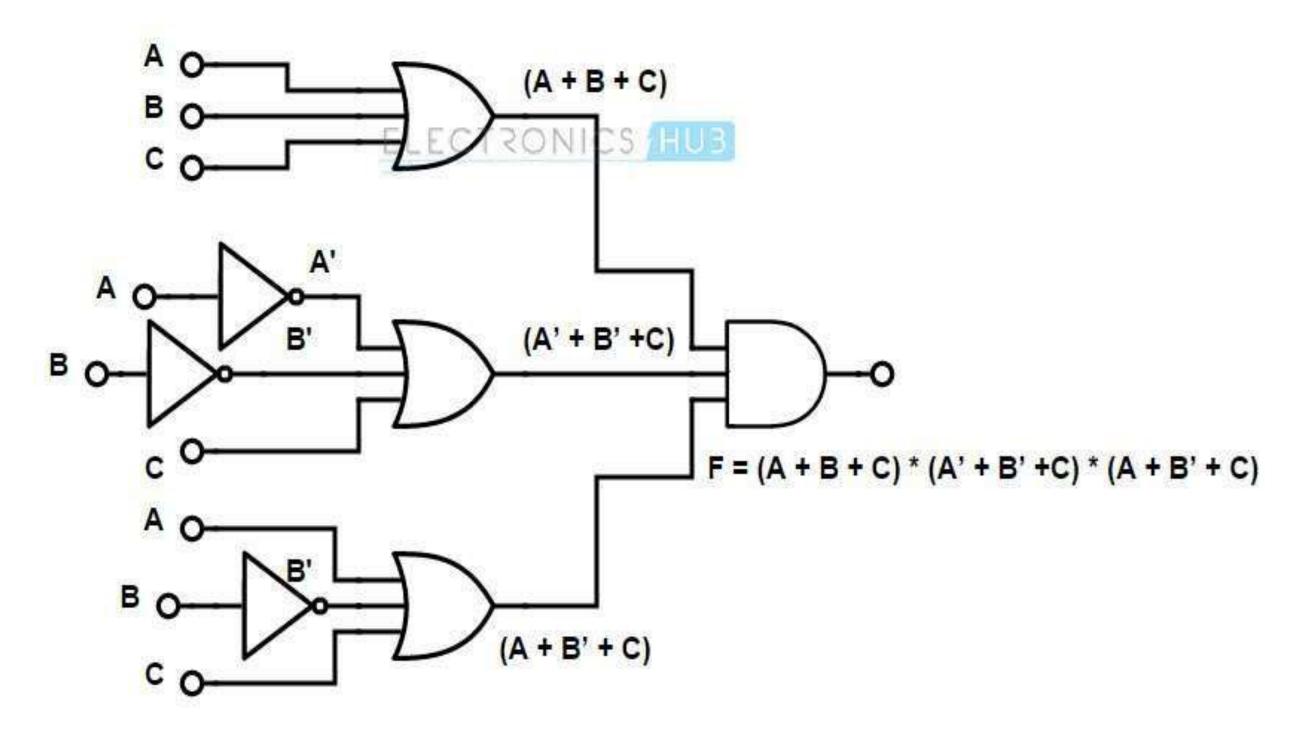

## **BOOLEAN EXPRESSION USING LOGIC GATES**

## **ASSESSMENTS**

- 1. What are universal gates? Why it is called so?

- 2.Draw the symbols and truth tablr of NOT gate and AND gate?

- 3.Draw the symbols of EXOR gate and explain its truth table.

# **THANK YOU**