## **SNS COLLEGE OF TECHNOLOGY**

Kurumbapalayam (Po), Coimbatore - 641 107

### **An Autonomous Institution**

Accredited by NBA – AICTE and Accredited by NAAC – UGC with AGrade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

COURSE NAME : 23CST202-OPERATING SYSTEMS

II YEAR / IV SEMESTER

#### Unit 1-OVERVIEW AND PROCESS MANAGEMENT

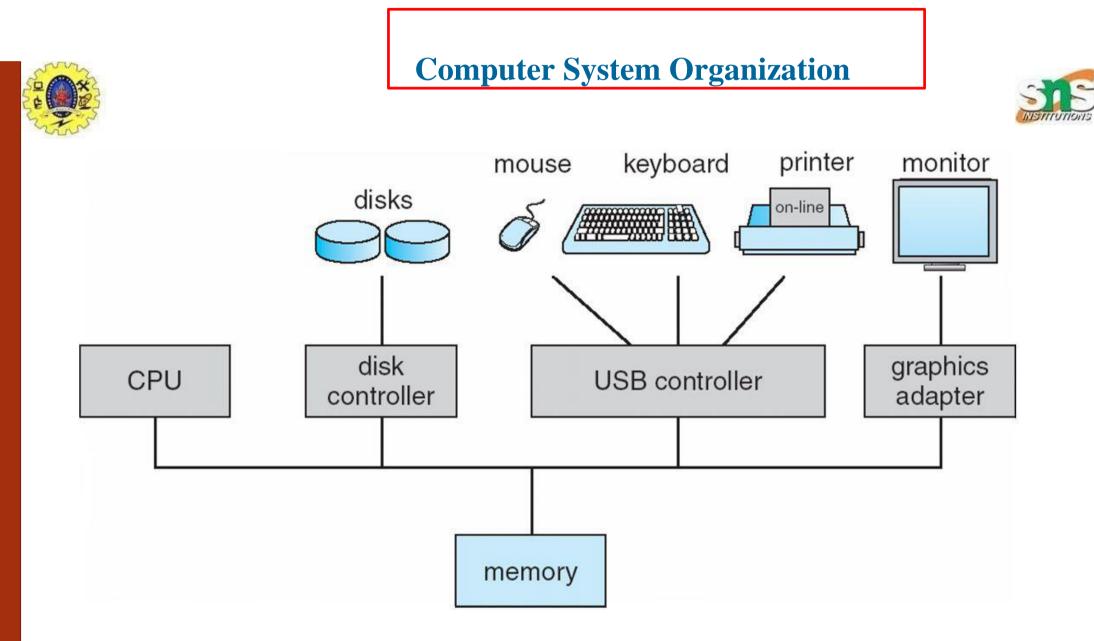

Topic : Computer System Organization

- One or more CPUs, device controllers connect through common bus providing access to shared memory

- Concurrent execution of CPUs and devices competing for memory cycles.

03/01/2025

OVERVIEW AND PROCESS MANAGEMENT/COMPUTER SYSTEM ORGANIZATION/ DURGALAKSHMI B/AIML/SNSCT

03/01/2025

OVERVIEW AND PROCESS MANAGEMENT/COMPUTER SYSTEM ORGANIZATION/ DURGALAKSHMI B/AIML/SNSCT

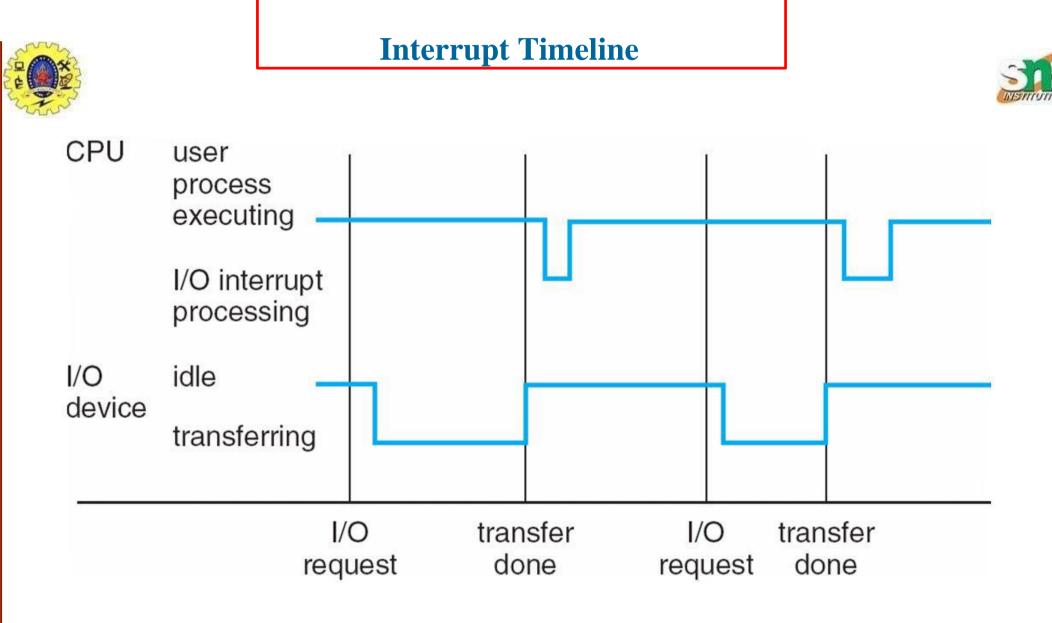

I/O devices and the CPU can execute concurrently

- Each device controller is in charge of a particular device type

- Each device controller has a local buffer

- CPU moves data from/to main memory to/from local buffers

- I/O is from the device to local buffer of controller

- Device controller informs CPU that it has finished its operation by causing an interrupt

• Interrupt transfers control to the interrupt service routine generally, through the

interrupt vector, which contains the addresses of all the service routines

- Interrupt architecture must save the address of the interrupted instruction

- A trap or exception is a software-generated interrupt caused either by an error or

a user request

• An operating system is **interrupt driven**

The operating system preserves the state of the CPU by

storing registers and the program counter

- Determines which type of interrupt has occurred:

- polling

- vectored interrupt system

Separate segments of code determine what action should

be taken for each type of interrupt

03/01/2025

OVERVIEW AND PROCESS MANAGEMENT/COMPUTER SYSTEM ORGANIZATION/ DURGALAKSHMI B/AIML/SNSCT

03/01/2025

OVERVIEW AND PROCESS MANAGEMENT/COMPUTER SYSTEM ORGANIZATION/ DURGALAKSHMI B/AIML/SNSCT

7

## **I/O Structure**

After I/O starts, control returns to user program only upon I/O completion

- Wait instruction idles the CPU until the next interrupt

- Wait loop (contention for memory access)

- At most one I/O request is outstanding at a time, no simultaneous I/O processing

- After I/O starts, control returns to user program without waiting for I/O completion

- System call request to the OS to allow user to wait for I/O completion

- **Device-status table** contains entry for each I/O device indicating its type, address, and state

- OS indexes into I/O device table to determine device

- status and to modify table entry to include interrupt OVERVIEW AND PROCESS MANAGEMENT/COMPUTER SYSTEM ORGANIZATION/

03/01/2025

OVERVIEW AND PROCESS MANAGEMENT/COMPUTER SY DURGALAKSHMI B/AIML/SNSCT

# THANK YOU