#### SNS COLLEGE OF TECHNOLOGY

(Autonomous )

COIMBATORE-35

- Incredible variety of I/O devices

- Storage

- Transmission

- Human-interface

- Common concepts signals from I/O devices interface with computer

- Port connection point for device

- Bus daisy chain or shared direct access

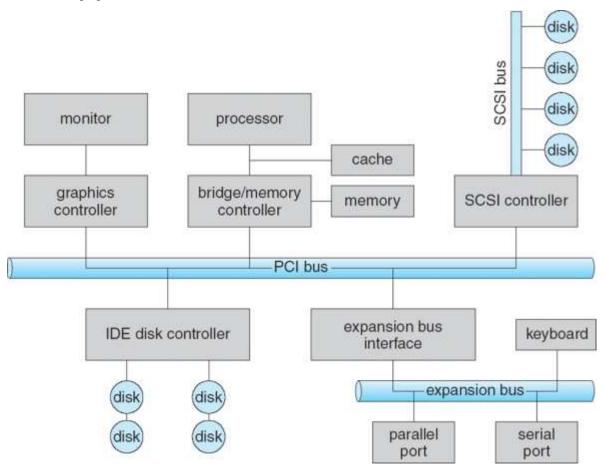

- PCI bus common in PCs and servers, PCI Express (PCIe)

- **expansion bus** connects relatively slow devices

- Controller (host adapter) electronics that operate port, bus, device

- Sometimes integrated

- Sometimes separate circuit board (host adapter)

- Contains processor, microcode, private memory, bus controller, etc

- Some talk to per-device controller with bus controller, microcode, memory, etc

#### A Typical PC Bus Structure

- Polling

- For each byte of I/O

- 1. Read busy bit from status register until 0

- 2. Host sets read or write bit and if write copies data into dataout register

- 3. Host sets command-ready bit

- 4. Controller sets busy bit, executes transfer

- 5. Controller clears busy bit, error bit, command-ready bit when transfer done

- Polling

- Step 1 is busy-wait cycle to wait for I/O from device

- Reasonable if device is fast

- But inefficient if device slow

- CPU switches to other tasks?

- But if miss a cycle data overwritten / lost

- Interrupts

- Polling can happen in 3 instruction cycles

- Read status, logical-and to extract status bit, branch if not zero

- HPow to be more efficient if non-zero infrequently?

- CPU Interrupt-request line triggered by I/O device

- Checked by processor after each instruction

- Interrupt handler receives interrupts

- Maskable to ignore or delay some interrupts

- Interrupts

- Interrupt vector to dispatch interrupt to correct handler

- Context switch at start and end

- Based on priority

- Some nonmaskable

- Interrupt chaining if more than one device at same interrupt number

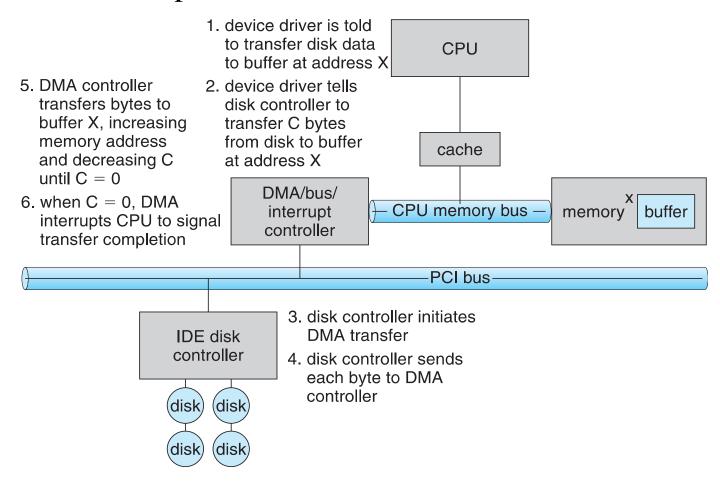

# I/O HARDWARE, DEVICE DRIVERS AND CONTROLLERS-Direct Memory Access

- Used to avoid **programmed I/O** (one byte at a time) for large data movement

- Requires **DMA** controller

- Bypasses CPU to transfer data directly between I/O device and memory

- OS writes DMA command block into memory

- Source and destination addresses

- Read or write mode

- Count of bytes

- Writes location of command block to DMA controller

- Bus mastering of DMA controller grabs bus from CPU

- Cycle stealing from CPU but still much more efficient

- When done, interrupts to signal completion

- Version that is aware of virtual addresses can be even more efficient DVMA

#### Six Step Process to Perform DMA Transfer

#### References

- 1. Silberschatz, Galvin, and Gagne, "Operating System Concepts", Ninth Edition, Wiley India Pvt Ltd, 2009.

- 2. Andrew S. Tanenbaum, "Modern Operating Systems", Fourth Edition, Pearson Education, 2010.

#### Summarization